The System Clock (SysClk) driver contains the API for configuring system and peripheral clocks.

The functions and other declarations used in this driver are in cy_sysclk.h. You can include cy_pdl.h to get access to all functions and declarations in the PDL.

Firmware uses the API to configure, enable, or disable a clock.

The clock system includes a variety of resources that can vary per device, including:

Consult the Technical Reference Manual for your device for details of the clock system.

The PDL defines clock system capabilities in:

devices/COMPONENT_CAT1<subcategory>/include/<series>_config.h. (E.g. devices/COMPONENT_CAT1A/include/psoc6_01_config.h).

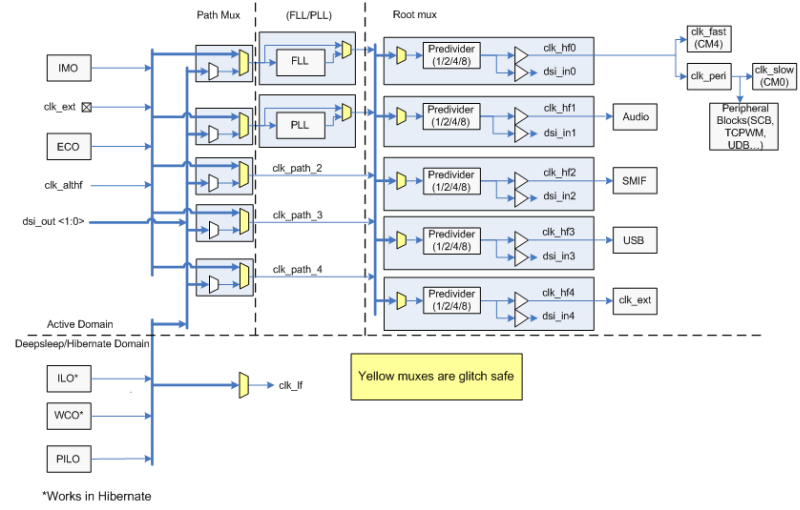

As an illustration of the clocking system, the following diagram shows the PSoC 63 series clock tree. The actual tree may vary depending on the device series. Consult the Technical Reference Manual for your device for details.

The sysclk driver supports multiple peripheral clocks, as well as the fast clock, slow clock, backup domain clock, timer clock, and pump clock. The API for any given clock contains the functions to manage that clock. Functions for clock measurement and trimming are also provided.

The availability of clock functions depend on the availability of the chip resources that support those functions. Consult the device TRM before attempting to use these functions. For PSoC 64 devices the clocks configurations are restricted and limited. Refer to the PRA driver, and the TRM and datasheet for details.

PSoC 6 power modes limit the maximum clock frequency. Refer to the SysPm driver and the TRM for details.

Refer to the technical reference manual (TRM) and the device datasheet.

| Version | Changes | Reason for Change |

|---|---|---|

| 3.150.1 | Updated description of the frequency range for Cy_SysClk_EcoSetFrequency and Cy_SysClk_EcoConfigure functions. | Defect fix. |

| 3.150 | Added support of Cy_SysClk_ClkLfGetFrequency API for MXS40SRSS ver. 2. | |

| 3.140 | Update PLL configuration for CAT1D devices. | |

| 3.130 | Corrects fractional enable behavior in Cy_SysClk_Pll400MConfigure. Only enables fractional divider if the fractional divider is non-zero. | |

| 3.120 | Added PSOC C3 device support. | New devices support added. |

| 3.110 | Added support for LPECO feature. Newly added APIs: Cy_SysClk_LpEcoConfigure() Cy_SysClk_LpEcoEnable() Cy_SysClk_LpEcoDisable() Cy_SysClk_LpEcoSetFrequency() Cy_SysClk_LpEcoGetFrequency() Cy_SysClk_LpEcoPrescaleConfigure() Cy_SysClk_LpEcoPrescaleIsEnabled() Cy_SysClk_LpEcoAmplitudeOkay() Cy_SysClk_LpEcoIsReady() | |

| 3.100 | Added support for CSV feature and fixed coverity bugs. | Added CSV feature support for CAT1D and bug fixes. |

| 3.90 | Added support for TRAVEO™ II Body Entry devices. Pre-processor check for MXS40SRSS version now groups ver. 2 with ver. 3. Previously ver. 2 was grouped with ver. 1. In cy_sysclk_v2 source, added pre-processor logic to include/exclude certain SRSS versions. Renamed PERI_DIV Defines to PERI_PCLK_GR_DIV for CAT1B and CAT1C. Changed pre-processor logic and set initial values to 0 for grpNum, instNum, locFrac, and locDiv variables to prevent uninitialized value access. Added pre-processor logic to prevent use of PLL400M API for non-compatible devices. Added "Unsupported Core Type" warning messages. In cy_sysclk_v2 source, added API Cy_SysClk_ClkFastGetDivider. | Code enhancement and support for new devices. |

| 3.80 | Added Cy_SysClk_PiloOkay new API and few macros. Updated Cy_SysClk_PiloEnable. | Usability enhancement. |

| 3.70 | Added new APIs Cy_SysClk_ClkPwrSetDivider, Cy_SysClk_ClkPwrGetDivider, Cy_SysClk_ClkPwrGetFrequency, Cy_SysClk_ClkPwrSetSource, Cy_SysClk_ClkPwrGetSource. and enum cy_en_clkpwr_in_sources_t | Support Added for future devices of the CAT1B. |

| 3.60 | Support for CAT1D devices is added | New devices support added |

| Remove local structure initialization to avoid optimization | Code cleanup | |

| 3.50 | Bug fixes and few new APIs addition. Newly added APIs: Cy_SysClk_PllGetFrequency() for CAT1A,CAT1C and CAT1D devices, Cy_SysClk_Pll200MGetFrequency() for CAT1C devices, Cy_SysClk_Pll400MGetFrequency() for CAT1C devices, Cy_SysClk_ImoEnable() for CAT1D devices, Cy_SysClk_ImoDisable() for CAT1D devices, Cy_SysClk_ImoIsEnabled() for CAT1D devices, Cy_SysClk_ImoDeepsleepEnable() for CAT1D devices, Cy_SysClk_ImoIsDeepsleepEnabled() for CAT1D devices, Cy_SysClk_ImoDeepsleepDisable() for CAT1D devices, Cy_SysClk_ClkFastSrcGetDivider() for CAT1C devices, Cy_SysClk_ClkFastSrcSetDivider() for CAT1C devices, Cy_SysClk_ClkFastSrcGetFrequency() for CAT1C devices, | Bug fixes and new devices support. |

| 3.40 | Added CAT1C and CAT1D devices support. | Support for new devices. |

| New API's for PLL400M and PLL200M. | To handle the new PLL's for CAT1C devices. | |

New API's Added

| New API's to handle CAT1B, CAT1C and CAT1D devices. | |

| 3.30 | For PSoC64 device, allow CM0+ to call CY_PRA_FUNCTION_CALL_X_X API in functions accessing FUNCTION_POLICY registers. So that System Configuration structure is updated with new parameters. | For PSoC64 device, System configuration can be done from CM0+ application. |

| Fixed MISRA 2012 violations. | MISRA 2012 compliance. | |

| Return type doxygen updated for PSoC64 devices. | Doxygen update for PSoC64 devices. | |

| 3.20 | Added new API's Cy_SysClk_FllGetFrequency and Cy_SysClk_PllGetFrequency. | Fetch the FLL and PLL frequency. |

| 3.10 | Support for CM33. | New devices support. |

| 3.0 | The behavior of Cy_SysClk_EcoEnable and Cy_SysClk_PllEnable is changed - these functions disable the resource in case of enabling failure (timeout). | Usability enhancement. |

| The implementation of Cy_SysClk_ClkPathGetSource, Cy_SysClk_FllConfigure, Cy_SysClk_FllGetConfiguration, Cy_SysClk_PllConfigure and Cy_SysClk_ClkMeasurementCountersGetFreq is updated in accordance to the MISRA 2012 requirements. No behavioral changes. | MISRA 2012 compliance. | |

| 2.20.1 | Updated source code comments. | Documentation update. |

| 2.20 | Added the assertion mechanism to the following functions:

Now, the functions described above halt in assertion when a PRA request returns not successful operation. This change is applicable only for the PSoC 64 family devices. | Enhancements for the debugging process. |

| Added Cy_SysClk_PiloInitialTrim and Cy_SysClk_PiloUpdateTrimStep functions. Extended the Cy_SysClk_PiloTrim function to use the step-size value calculated for PILO based on the Cy_SysClk_PiloInitialTrim and Cy_SysClk_PiloUpdateTrimStep functions call. | User experience enhancement. | |

| Documentation updates. | |

| 2.10 | Updated SysClk functions for PSoC 64 devices. Now the SysClk functions can return PRA driver status value. | The SysClk driver uses the PRA driver to change the protected registers. A SysClk driver function that calls a PRA driver function will return the PRA error status code if the called PRA function returns an error. In these cases, refer to PRA return statuses. Refer to functions description for details. |

| Updated the code of Cy_SysClk_ClkPathGetFrequency function. | Make the code more error-resistant to user errors for some corner cases. | |

| Minor documentation updates. | Documentation enhancement. | |

| 2.0 | Updated the ECO trimming values calculation algorithm in the Cy_SysClk_EcoConfigure implementation. This change may invalidate the already used crystals, in cases:

| Enhanced the ECO performance for high-noise conditions that result from simultaneous switching of GPIOs and/or high switching activity on the chip. |

| 1.60 | Added the following functions: Cy_SysClk_ExtClkGetFrequency, Cy_SysClk_EcoGetFrequency, Cy_SysClk_ClkPathMuxGetFrequency, Cy_SysClk_ClkPathGetFrequency, Cy_SysClk_IloIsEnabled. Cy_SysClk_PiloIsEnabled, Cy_SysClk_AltHfGetFrequency, Cy_SysClk_ClkHfIsEnabled, Cy_SysClk_ClkTimerIsEnabled, Cy_SysClk_ClkTimerGetFrequency, Cy_SysClk_ClkPumpIsEnabled and Cy_SysClk_ClkPumpGetFrequency. | API enhancement. |

| 1.50 | Cy_SysClk_ClkHfGetFrequency is updated to reuse the cy_BleEcoClockFreqHz global system variable. | API enhancement. |

| 1.40.2 | Update documentation based on collateral review feedback. | User experience enhancement. |

| 1.40.1 | Fix compiler warning. | |

| 1.40 | Updated the following functions implementation: Cy_SysClk_PllConfigure and Cy_SysClk_PllEnable. | Fixed the Cy_SysClk_PllConfigure API function behaviour when it is called with a bypass mode, Fixed the Cy_SysClk_PllEnable API function behaviour when it is called with a zero timeout. |

| Added the following functions: Cy_SysClk_MfoEnable, Cy_SysClk_MfoIsEnabled, Cy_SysClk_MfoDisable, Cy_SysClk_ClkMfEnable, Cy_SysClk_ClkMfIsEnabled, Cy_SysClk_ClkMfDisable, Cy_SysClk_ClkMfGetDivider, Cy_SysClk_ClkMfSetDivider, . Cy_SysClk_ClkMfGetFrequency | New device support. | |

| Added the following new API functions Cy_SysClk_FllIsEnabled, Cy_SysClk_PllIsEnabled, Cy_SysClk_ExtClkSetFrequency, Cy_SysClk_ClkHfGetFrequency, Cy_SysClk_ClkFastGetFrequency, Cy_SysClk_ClkPeriGetFrequency and Cy_SysClk_ClkSlowGetFrequency | Enhancement based on usability feedback | |

| Deprecated the following macros: CY_SYSCLK_DIV_ROUND and CY_SYSCLK_DIV_ROUNDUP | Macros were moved into SysLib (System Library) | |

| 1.30 | Updated the following functions implementation: Cy_SysClk_EcoConfigure and Cy_SysClk_FllConfigure. | Math library dependency is removed, the floating-point math is replaced with integer math. |

| Updated the following functions implementation: Cy_SysClk_EcoEnable, Cy_SysClk_EcoGetStatus, Cy_SysClk_FllGetConfiguration and Cy_SysClk_DeepSleepCallback. The Cy_SysClk_DeepSleepCallback now implements all four SysPm callback modes cy_en_syspm_callback_mode_t. The actions that were done in CY_SYSPM_CHECK_READY case are moved to CY_SYSPM_BEFORE_TRANSITION. So the cy_stc_syspm_callback_t::skipMode must be set to 0UL. | Defect fixing. | |

| 1.20 | Flattened the organization of the driver source code into the single source directory and the single include directory. | Driver library directory-structure simplification. |

| Updated Cy_SysClk_FllLocked function description | The SRSS_ver1 HW details clarification | |

Removed the following functions:

| No hardware support for the removed functions. | |

| Added register access layer. Use register access macros instead of direct register access using dereferenced pointers. | Makes register access device-independent, so that the PDL does not need to be recompiled for each supported part number. | |

| 1.11 | Updated the following functions. Now they use a semaphore when try to read the status or configure the SysClk measurement counters: Now Cy_SysClk_ClkMeasurementCountersGetFreq() returns zero value, if during measurement device was in the Deep Sleep or partially blocking flash operation occurred | Added arbiter mechanism for correct usage of the SysClk measurement counters |

| 1.10.1 | Renamed Power Management section to Low Power Callback section | Documentation update and clarification |

| 1.10 | Updated FLL parameter calculation | Support low frequency sources |

| Added Cy_SysClk_PiloSetTrim() and Cy_SysclkPiloGetTrim() functions | Support PILO manual trims | |

| Made Cy_SysClk_FllLostLock() function dependent on SRSS v1 | Feature is not supported in SRSS v1 | |

| Updated Cy_SysClk_DeepSleepCallback() to save/restore both FLL and PLL settings | The function should return when the lock is established or a timeout has occurred | |

| General documentation updates | ||

| 1.0 | Initial version |

API Reference | |

| Macros | |

| General Enumerated Types | |

| External Clock Source (EXTCLK) | |

| The External Clock Source (EXTCLK) is a clock source routed into SOC through a GPIO pin. | |

| External Crystal Oscillator (ECO) | |

| The External Crystal Oscillator (ECO) is a clock source that consists of an oscillator circuit that drives an external crystal through its dedicated ECO pins. | |

| Clock Path Source | |

| Clock paths are a series of multiplexers that allow a source clock to drive multiple clocking resources down the chain. | |

| Frequency Locked Loop (FLL) | |

| The FLL is a clock generation circuit that can be used to produce a higher frequency clock from a reference clock. | |

| Phase Locked Loop (PLL) | |

| The PLL is a clock generation circuit that can be used to produce a higher frequency clock from a reference clock. | |

| Internal Low-Speed Oscillator (ILO) | |

| The ILO operates with no external components and outputs a stable clock at 32.768 kHz nominal. | |

| Precision Internal Low-Speed Oscillator (PILO) | |

| PILO provides a higher accuracy 32.768 kHz clock than the ILO. | |

| Clock Measurement | |

| These functions measure the frequency of a specified clock relative to a reference clock. | |

| Clock Trim (ILO, PILO) | |

| These functions perform a single trim operation on the ILO or PILO. | |

| Low Power Callback | |

| Entering and exiting low power modes require compatible clock configurations to be set before entering low power and restored upon wake-up and exit. | |

| Watch Crystal Oscillator (WCO) | |

| The WCO is a highly accurate 32.768 kHz clock source capable of operating in all power modes (excluding the Off mode). | |

| Low-Power External Crystal Oscillator (LPECO) | |

| The LPECO provides high-frequency clocking using an external crystal connected to the LPECO_IN and LPECO_OUT pins. | |

| High-Frequency Clocks | |

| Multiple high frequency clocks (CLK_HF) are available in the device. | |

| Fast Clock | |

| The fast clock drives the "fast" processor (e.g. | |

| Peripheral Clock | |

| The peripheral clock is a divided clock of CLK_HF0 (HF Clocks). | |

| Peripherals Clock Dividers | |

| There are multiple peripheral clock dividers that, in effect, create multiple separate peripheral clocks. | |

| Peripheral Group(MMIO Group) Controls | |

| All the peripherals in the SOC belongs to certain MMIO groups. | |

| Slow Clock | |

| The slow clock is the source clock for the "slow" processor (e.g. | |

| Alternative High-Frequency Clock | |

| In the BLE-enabled PSoC6 devices, the BLE ECO (Bluetooth® LE ECO Clock) clock is connected to the system Alternative High-Frequency Clock input. | |

| Low-Frequency Clock | |

| The low-frequency clock is the source clock for the MCWDT (Multi-Counter Watchdog) and can be the source clock for Backup Domain Clock, which drives the RTC (Real-Time Clock). | |

| Timer Clock | |

| The timer clock can be a source for the alternative clock driving the SysTick (Arm® System Timer). | |

| Pump Clock | |

| The pump clock is a clock source used to provide analog precision in low voltage applications. | |

| Backup Domain Clock | |

| The backup domain clock drives the RTC (Real-Time Clock). | |

| Medium Frequency Domain Clock | |

| The Medium Frequency Domain Clock is present only in SRSS_ver1_3. | |

| Internal High Frequency(IHO) Clock | |

| The IHO Clock is Internal High-speed Oscillator, which is present in CAT1B(48MHz) and CAT1D(50MHz) devices. | |

| Internal Main Oscillator(IMO) Clock | |

| The IMO Clock is Internal Main Oscillator, which is present in CAT1A/CAT1B/CAT1C and CAT1D devices, where as it is it is 8MHz in CAT1A/CAT1B/CAT1C, and CAT1D supports two instances of IMO i.e. | |

| Mem Clock | |

| Clock for the Memories. | |

| Power Clock | |

| Clock for the power architecture components. | |

| Group_sysclk_clk_ref_enums | |

| Group_sysclk_clk_ref_structs | |

| Group_sysclk_clk_ref_funcs | |

| Group_sysclk_clk_ilo_enums | |

| Group_sysclk_clk_ilo_structs | |

| Group_sysclk_clk_ilo_funcs | |