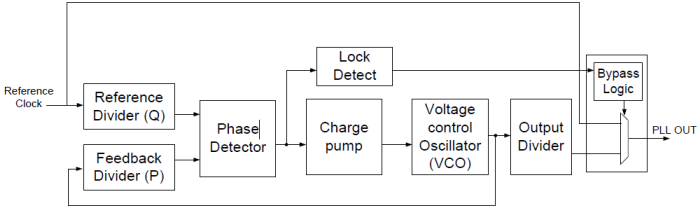

The PLL is a clock generation circuit that can be used to produce a higher frequency clock from a reference clock.

The output clock exhibits characteristics of the reference clock such as the accuracy of the source and its phase. The PLL is similar in purpose to a (Frequency locked loop) FLL but they are not equivalent.

The SysClk driver supports two models for configuring the PLL. The first model is to call the Cy_SysClk_PllConfigure() function, which calculates the necessary parameters for the PLL at run-time. This may be necessary for dynamic run-time changes to the PLL. However this method is slow as it needs to perform the calculation before configuring the PLL. The other model is to call Cy_SysClk_PllManualConfigure() function with pre-calculated parameter values. This method is faster but requires prior knowledge of the necessary parameters. Consult the device TRM for the PLL calculation equations.

API Reference | |

| Functions | |

| Data Structures | |

| Enumerated Types | |