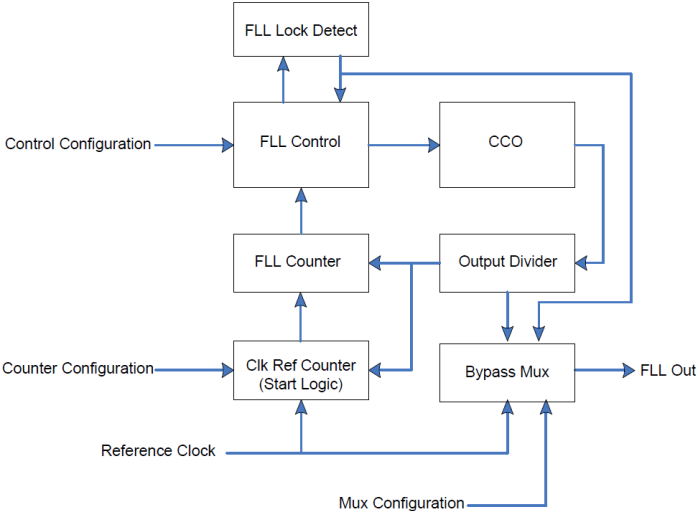

The FLL is a clock generation circuit that can be used to produce a higher frequency clock from a reference clock.

The output clock exhibits some characteristics of the reference clock such as the accuracy of the source. However other attributes such as the clock phase are not preserved. The FLL is similar in purpose to a (Phase locked loop) PLL but they are not equivalent.

The SysClk driver supports two models for configuring the FLL. The first model is to call the Cy_SysClk_FllConfigure() function, which calculates the necessary parameters for the FLL at run-time. This may be necessary for dynamic run-time changes to the FLL. However this method is slow as it needs to perform the calculation before configuring the FLL. The other model is to call Cy_SysClk_FllManualConfigure() function with pre-calculated parameter values. This method is faster but requires prior knowledge of the necessary parameters. Consult the device TRM for the FLL calculation equations.

API Reference | |

| Functions | |

| Data Structures | |

| Enumerated Types | |