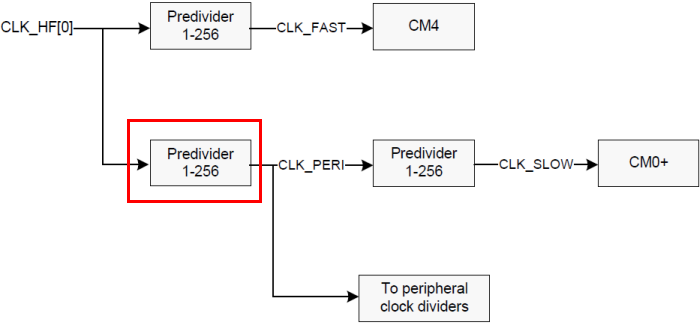

The peripheral clock is a divided clock of CLK_HF0 (HF Clocks).

It is the source clock for the Slow Clock, and most active domain peripheral clocks (Peripherals Clock Dividers). A divider value of 1~256 can be used to further divide the CLK_HF[0] to a desired clock speed for the peripherals.

API Reference | |

| Functions | |