This driver provides API functions to configure the Comparator Slope Generator within High Power Programmable Analog Sub-System.

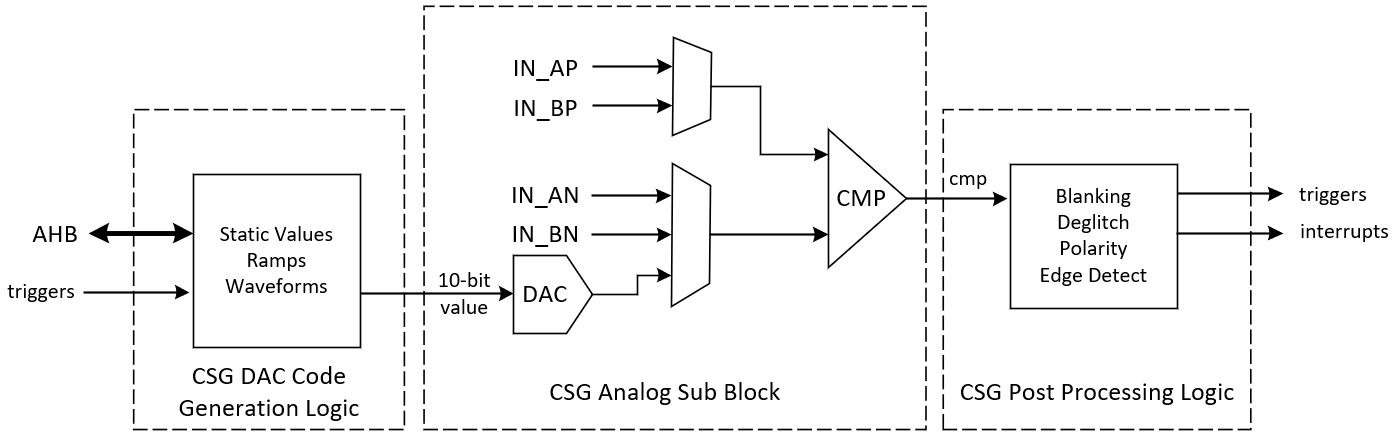

The CSG is a flexible block which compares a 10-bit DAC value with a selected analog input signal or compares two analog inputs. The output of this block is the 1-bit digital compare value that can be used for controlling the behavior of the TCPWM in a motor control, power conversion and other applications.

The CSG block contains 5 CSG slices (for PSOC C3 devices), each of which can be configured and used independently. Each slice contains a DAC and a comparator with the dedicated control logic. The internal structure and external HW interface of the CSG slice are shown below.

DAC

The user has various options to control the DAC data:

- Single value buffered mode

- Two value hysteretic buffered mode

- Slope mode (rising, falling, triangular) with programmable slope rate

- Look-Up Table (LUT) mode with programmable data (128 samples).

DAC data update can be triggered by either a HW or FW trigger. Available HW DAC trigger sources:

- Any of the 8 HPPASS triggers

- DAC divider

- CSG comparator local output

- AC trigger.

Comparator

The Comparator can be configured to compare a signal from the dedicated analog input or from the DAC output to another selected analog input.

The CSG comparator output signal has the following post-processing options:

- Direct output/inverted output

- Gated output by the blanking trigger

- Edge detection for the interrupt generation

- Trigger generation for the Autonomous Controller.

CSG Interrupts

The HPPASS CSG block provides DAC and comparator interrupts to the CPU interrupt controller.

DAC Interrupts

A DAC interrupt is generated on the following events:

- DAC hardware start trigger

- DAC slope/LUT operation completed

- DAC buffer empty

The DAC interrupts should be enabled by setting the corresponding mask in the HPPASS_CSG_DAC_INTR_MASK register using Cy_HPPASS_DAC_SetInterruptMask function. To determine which DAC slice generated the interrupt, read the HPPASS_CSG_DAC_INTR_MASKED register using Cy_HPPASS_DAC_GetInterruptStatusMasked function. To clear the DAC interrupt, use Cy_HPPASS_DAC_ClearInterrupt function.

The CSG provides both individual interrupts for each of the five DAC slices (pass_interrupt_csg_dac_0..4_IRQn) and a combined DAC interrupt (pass_interrupt_csg_dacs_IRQn). When using the combined interrupt, the HPPASS_CSG_DAC_INTR register must be read using Cy_HPPASS_DAC_GetInterruptStatus function to determine the cause of the interrupt.

Comparator Interrupts

The CSG comparators provide only a combined interrupt.

The comparator interrupt can be generated on rising, falling, or both edges of the comparator output. The edge selection is configured in the comparator configuration structure cy_stc_hppass_comp_t::edge field. The selected comparator interrupt should be enabled by setting the corresponding mask in the HPPASS_CSG_CMP_INTR_MASK register using Cy_HPPASS_Comp_SetInterruptMask function. To determine which comparator generated the interrupt, read the HPPASS_CSG_CMP_INTR_MASKED register using Cy_HPPASS_Comp_GetInterruptStatusMasked function. To clear the comparator interrupt, use Cy_HPPASS_Comp_ClearInterrupt function.

CSG Configuration

To configure the CSG, the driver uses a configuration structure of type cy_stc_hppass_csg_t that must be predefined. This structure holds the pointer to the array of CSG slices configuration structures cy_stc_hppass_slice_t, as well the pointer to the array of the CSG LUT configuration structures cy_stc_hppass_lut_t. Also, this structure contains the DAC output selector field cy_en_hppass_dac_out_t, which routes the selected DAC output to the HPPASS SAR input for debugging purposes.

- Note

- The total number of LUTs is 2 for the PSOC C3 devices, but the same LUT can be used by multiple CSG slices. LUT 0 can be used by CSG slices 0, 1, and 2; LUT 1 by slices 3 and 4.

Each instance of the cy_stc_hppass_slice_t contains the comparator configuration structure cy_stc_hppass_comp_t and the DAC configuration structure cy_stc_hppass_dac_t.

Refer to the Technical Reference Manual for detailed information.

Code Snippets

CSG Analog to PWM conversion

The example below shows how to configure the CSG slice to generate PWM signal on P7_0 with the duty cycle proportional to the analog input voltage on the AN_A0 pin.

- Configure the CSG slice 0 to:

- Generate a repeating rising slope from 0 to VDDA on DAC 0

- Use AN_A0 pin as the positive comparator input and the DAC output as the negative comparator input.

{

{

.invert = false,

},

.dac =

{

.continuous = true,

.skipTrig = false,

.cascade = false,

.paramSync = false,

.stepSize = 1U,

.deGlitch = 0U,

.valBuffA = 0U,

.valBuffB = 1023U,

.period =

{

.frac = 23U,

.intg = 11U,

},

}

};

- Note

- The cy_stc_hppass_slice_t::dac::period field is calculated to update the DAC at the frequency of 10240 kHz for CSG clock = 120 MHz. For the the 1024 rising slope values (0 to 1023), the slope period will be 10240 kHz / 1024 = 10 kHz. The HPPASS CSG Slice Personality in the Device Configurator includes the calculator for the DAC period value.

- Configure the CSG block with the CSG slice 0 configuration:

{

.

slice = {&slice0Cfg, NULL, NULL, NULL, NULL},

.dacOut = 0U,

.lut = {NULL, NULL}

};

- Configure the Autonomous Controller (AC) STT to start the CSG slice 0 and then stop the AC:

{

{

.branchStateIdx = 0U,

.interrupt = false,

.count = 1U,

.gpioOutUnlock = false,

.gpioOutMsk = 0U,

.csgUnlock = {true, false, false, false, false},

.csgEnable = {true, false, false, false, false},

.csgDacTrig = {false, false, false, false, false},

.sarUnlock = false,

.sarEnable = false,

.sarGrpMsk = 0U,

.sarMux = {{0}, {0}, {0}, {0}}

}

};

- Complete the HPPASS configuration with the HPPASS startup and triggers configuration. The output level trigger 0 is used to route the CSG Slice 0 comparator output to the output pin:

{

{

.stt = stateTransitionTable,

.gpioOutEnMsk = 0U,

.startupClkDiv = 24U,

.startup =

{

{

.sar = true,

.csgChan = true,

.csgSlice = false,

.csgReady = false,

},

{

.count = 50U,

.sar = false,

.csgChan = false,

.csgSlice = true,

.csgReady = false,

},

{

.count = 1U,

.sar = false,

.csgChan = false,

.csgSlice = false,

.csgReady = true,

},

{

.count = 0U,

.sar = false,

.csgChan = false,

.csgSlice = false,

.csgReady = false,

},

},

},

.csg = &csgCfg,

.sar = NULL,

.trigIn = {{0}, {0}, {0}, {0}, {0}, {0}, {0}, {0}},

.trigLevel =

{

{

.syncBypass = false,

},

{0}, {0}, {0}, {0}, {0}, {0}, {0}

}

};

- Note

- Only usage of the startup parameters recommended by the vendor guarantees the reliable operation of the Autonomous Controller.

Please use the Device Configurator tool to make configurations or refer to the Technical Reference Manual for detailed information.

- Configure the GPIO pin P7_0 as an output and connect it to the HPPASS Output Level Trigger 0 using TrigMux:

Cy_TrigMux_Connect(TRIG_IN_MUX_2_PASS_LEVEL0, TRIG_OUT_MUX_2_HSIOM_TR_IO_OUTPUT30,

false, TRIGGER_TYPE_LEVEL);

- Enable and assign divider 1 to the CSG with the frequency = CLK_HF3 / 2:

- Initialize the HPPASS block and the Autonomous Controller:

{

CY_ASSERT(0);

}

{

CY_ASSERT(0);

}

- Wait for the Autonomous Controller to be ready:

- Start DAC 0 slope generation: