Configures a DMA channel and its descriptor(s).

The functions and other declarations used in this driver are in cy_dma.h. You can include cy_pdl.h to get access to all functions and declarations in the PDL.

The DMA channel can be used in any project to transfer data without CPU intervention basing on a hardware trigger signal from another component.

A device may support more than one DMA hardware block. Each block has a set of registers, a base hardware address, and supports multiple channels. Many API functions for the DMA driver require a base hardware address and channel number. Ensure that you use the correct hardware address for the DMA block in use.

Features:

To set up a DMA driver, initialize a descriptor, initialize and enable a channel, and enable the DMA block.

To set up a descriptor, provide the configuration parameters for the descriptor in the cy_stc_dma_descriptor_config_t structure. Then call the Cy_DMA_Descriptor_Init function to initialize the descriptor in SRAM. You can modify the source and destination addresses dynamically by calling Cy_DMA_Descriptor_SetSrcAddress and Cy_DMA_Descriptor_SetDstAddress.

To set up a DMA channel, provide a filled cy_stc_dma_channel_config_t structure. Call the Cy_DMA_Channel_Init function, specifying the channel number. Use Cy_DMA_Channel_Enable to enable the configured DMA channel.

Call Cy_DMA_Channel_Enable for each DMA channel in use.

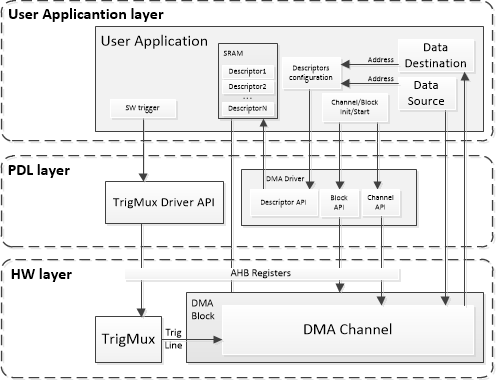

When configured, another peripheral typically triggers the DMA. The trigger is connected to the DMA using the trigger multiplexer. The trigger multiplexer driver has a software trigger you can use in firmware to trigger the DMA. See the Trigger Multiplexer documentation.

The following is a simplified structure of the DMA driver API interdependencies in a typical user application:

NOTE: Even if a DMA channel is enabled, it is not operational until the DMA block is enabled using function Cy_DMA_Enable.

NOTE: If the DMA descriptor is configured to generate an interrupt, the interrupt must be enabled using the Cy_DMA_Channel_SetInterruptMask function for each DMA channel.

For example:

See: the DMA chapter of the device technical reference manual (TRM); the DMA Component datasheet; CE219940 - PSoC 6 MCU Multiple DMA Concatenation.

The DMA driver has the following specific deviations:

| MISRA Rule | Rule Class (Required/Advisory) | Rule Description | Description of Deviation(s) |

|---|---|---|---|

| 10.3 | R | A composite expression of the "essentially unsigned" type is being cast to a different type category. | The value got from the bitfield physically cannot exceed the enumeration that describes this bitfield. So, the code is safe by design. |

| 11.4 | A | A cast should not be performed between a pointer to object type and a different pointer to object type. | This piece of code is written for DW_V2_Type only and it will be never executed for DW_V1_Type (which is a default build option for DW_Type). |

| Version | Changes | Reason for Change |

|---|---|---|

| 2.20.1 | Minor documentation updates. | Documentation enhancement. |

| 2.20 | The channel number validation method is updated. | New devices support. |

| 2.10 | Flattened the organization of the driver source code into the single source directory and the single include directory. | Driver library directory-structure simplification. |

| Added CRC mode and the CRC descriptor support. Added the Cy_DMA_Crc_Init function. | New devices support. | |

| Added register access layer. Use register access macros instead of direct register access using dereferenced pointers. | Makes register access device-independent, so that the PDL does not need to be recompiled for each supported part number. | |

| 2.0.1 | Changed CY_DMA_BWC macro values from Boolean to numeric | Improvements made based on usability feedback |

| 2.0 | * All the API is refactored to be consistent within itself and with the rest of the PDL content.

| |

| 1.0 | Initial version |

API Reference | |

| Macros | |

| Functions | |

| Data Structures | |

| Enumerated Types | |