The SPI-based communication interface to the external quad SPI (QSPI) high-speed memory devices.

The functions and other declarations used in this driver are in cy_smif.h and cy_smif_memslot.h (if used). If you are using the ModusToolbox QSPI Configurator, also include cycfg_qspi_memslot.h.

SMIF: Serial Memory Interface: This IP block implements an SPI-based communication interface for interfacing external memory devices to PSoC. The SMIF supports SPI, dual SPI (DSPI), quad SPI (QSPI), dual QSPI and octal SPI.

Features

The primary usage model for the SMIF is that of an external memory interface. The SMIF is capable of interfacing with different types of memory, up to four types.

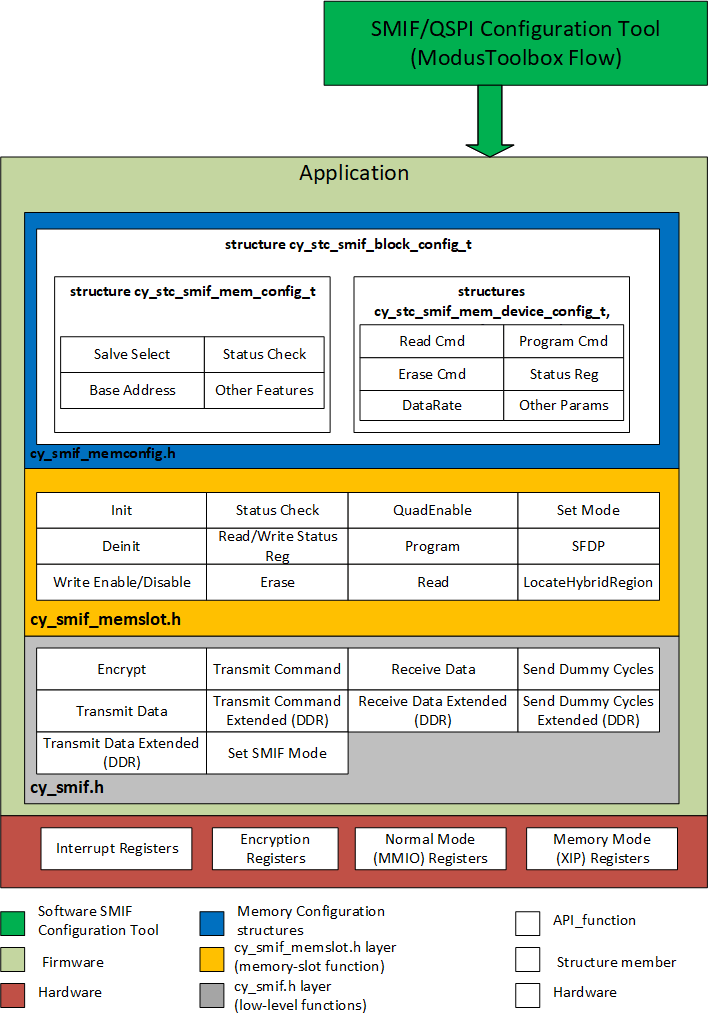

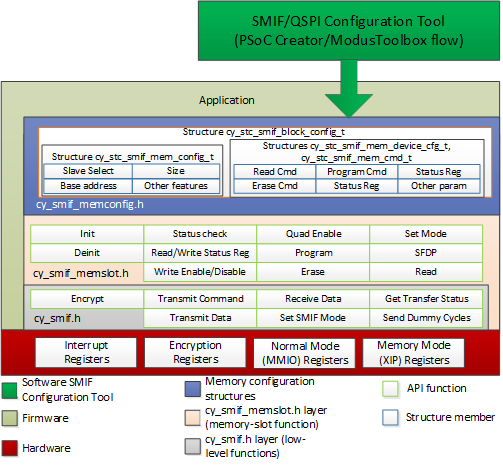

SMIF driver is divided into three layers

The SMIF API is divided into the low-level functions and memory-slot functions. Use the low level API for the SMIF block initialization and for implementing a generic SPI communication interface using the SMIF block.

The memory slot API has functions to implement the basic memory operations such as program, read, erase etc. These functions are implemented using the memory parameters in the memory device configuration data structure. The Cy_SMIF_MemInit() API initializes all the memory slots based on the settings in the array.

SMIF Configuration Tool is a stand-alone application, which is a part of PDL (Creator) and could be found in <PDL_DIR>/tools/<OS_DIR>/SMIFConfigurationTool (e.g. for PDL 3.0.0 and Windows OS PDL/3.0.0/tools/win/SMIFConfigurationTool).

In ModusToolbox this tool is called QSPI Configurator. QSPI Configurator is a part of PSoC 6 Software Library and can be found in <ModusToolbox>/tools/qspi-configurator-1.1

Tool generates *.c and *.h file with configuration structures. These configuration structures are input parameters for cy_smif_memslot API level

For the Write operation, check that the SMIF driver has completed transferring by calling Cy_SMIF_BusyCheck(). Also, check that the memory is available with Cy_SMIF_MemIsBusy() before proceeding.

Simple example of external flash memory programming using low level SMIF API. All steps mentioned in example below are incorporated in Cy_SMIF_MemCmdWriteEnable(), Cy_SMIF_MemCmdProgram(), and Cy_SMIF_MemIsBusy() of the memory slot level API.

For the Read operation, before accessing the read buffer, check that it is ready by calling Cy_SMIF_GetTxFifoStatus().

Simple example of external flash memory read using low level SMIF API. All steps mentioned in example below are incorporated in Cy_SMIF_MemCmdRead() of the memory slot level API.

The user should invalidate the cache by calling Cy_SMIF_CacheInvalidate() when switching from the MMIO mode to XIP mode.

PDL API has common parameters: base, context, config described in PDL Design section.

See the documentation for Cy_SMIF_Init() and Cy_SMIF_MemInit() for details on the required configuration structures and other initialization topics.

The normal (MMIO) mode is used for implementing a generic SPI/DSPI/QSPI/dual QSPI/octal SPI communication interface using the SMIF block. This interface can be used to implement special commands like Program/Erase of flash, memory device configuration, sleep mode entry for memory devices or other special commands specific to the memory device. The transfer width (SPI/DSPI/QSPI/octal SPI) of a transmission is a parameter set for each transmit/receive operation. So these can be changed at run time.

In a typical memory interface with flash memory, the SMIF is used in the memory mode when reading from the memory and it switches to the normal mode when writing to flash memory. A typical memory device has multiple types of commands.

The SMIF interface can be used to transmit different types of commands. Each command has different phases: command, dummy cycles, and transmit and receive data which require separate APIs.

Create interrupt function and allocate memory for SMIF context structure

SMIF driver initialization for low level API usage (cysmif.h)

Additional steps to initialize SMIF driver for memory slot level API usage (cy_smif_memslot.h).

The eXecute In Place (XIP) is a mode of operation where read or write commands to the memory device are directed through the SMIF without any use of API function calls. In this mode the SMIF block maps the AHB bus-accesses to external memory device addresses to make it behave similar to internal memory. This allows the CPU to execute code directly from external memory. This mode is not limited to code and is suitable also for data read and write accesses. The memory regions available for XIP addresses allocation are defined in a linker script file (.ld).

With SMIF V3 IP, MMIO mode transactions are also allowed when the device is set to XIP mode. However, only blocking SMIF API's are expected to be used for erase or program operations as external flash will be busy for such operation and may not be available for XIP at that moment. User can make use of Cy_SMIF_MemRead, Cy_SMIF_MemWrite, Cy_SMIF_MemEraseSector API's which ensure that user gets control only after completing the requested operation. This will ensure the transaction is complete and then switch back to XIP. In case user wishes to make use of low level API's like Cy_SMIF_TransmitCommand_Ext, Cy_SMIF_TransmitData_Ext, Cy_SMIF_SendDummyCycles_Ext user has to ensure the code is not running already from XIP location and complete the operation before switching back to XIP mode of execution. Also, user has to bound his complete SMIF operation using Cy_SysLib_EnterCriticalSection and Cy_SysLib_ExitCriticalSection so that there is no interruption for the operation due to any other interrupts.

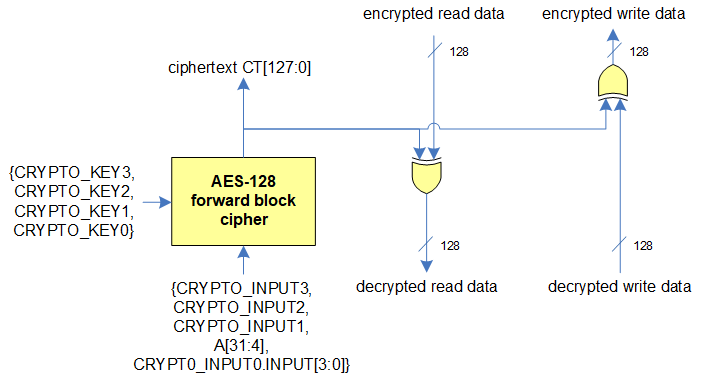

In XIP mode, a cryptography component supports on-the-fly encryption for write data and on-the-fly decryption for read data. On-the-fly encryption/decryption in XIP mode can be enabled by setting the flags CY_SMIF_FLAG_CRYPTO_ENABLE. Encryption and decryption are based on the AES-128 forward block cipher: advanced encryption standard blockcipher with a 128-bit key. KEY[127:0] is a secret (private) key programmed into the CRYPTO_KEY3,...,CRYPTO_KEY0 registers using Cy_SMIF_SetCryptoKey. These registers are software write-only. A software read returns 0. In the SMIF hardware, by applying AES-128 with KEY[127:0] on a plaintext PT[127:0], we get a ciphertext CT[127:0]. In XIP mode, the XIP address is used as the plaintext PT[]. The resulting ciphertext CT[] is used on-the-fly and not software accessible. The XIP address is extended with the CRYPTO_INPUT3, ..., CRYPTO_INPUT0 registers. Cy_SMIF_SetCryptoIV can be used to set initialization vector (96-bits). In XIP mode, the resulting ciphertext CT[] (of the encrypted address) is XORed with the memory transfers read data or write data. Note that the AES-128 block cipher is on the address of the data and not on the data itself.

More information regarding the Serial Memory Interface can be found in the component datasheet and the Technical Reference Manual (TRM). More information regarding the SMIF Configuration Tool are in SMIF Configuration Tool User Guide located in <PDL_DIR>/tools/<OS_DIR>/SMIFConfigurationTool/ folder

| Version | Changes | Reason for Change |

|---|---|---|

| 2.140 | New device support added for TRAVEO T2G CYT3DL. | New Device support added. |

| 2.130 | Updated APIs : Cy_SMIF_Init, Cy_SMIF_InitCache, Cy_SMIF_Clean_All_Cache, Cy_SMIF_Invalidate_All_Cache, Cy_SMIF_Clean_And_Invalidate_All_Cache, Cy_SMIF_Clean_Cache_by_Addr, Cy_SMIF_Invalidate_Cache_by_Addr Cy_SMIF_Clean_And_Invalidate_Cache_by_Addr, Cy_SMIF_MemInitSfdpMode. | Updated secure interface to Align secure services with TFM and Bug Fixes |

| 2.120 | Added APIs for MDL and SDL tap settings: Cy_SMIF_Set_DelayTapSel Cy_SMIF_Set_Sdl_DelayTapSel CY_SMIF_GetDelayTapsNumber Added APIs for SMIF Bridge enablement: Cy_SMIF_IsBridgeOn Cy_SMIF_Bridge_Enable Added configurable TX SDR Extra support during SMIF initialized. | New device support added for Traveo II Cluster. |

| 2.110 | Added PSOC C3 device support. | New Device support added. |

| 2.100 | Updated slaveSelect validity check to allow Dual QSPI use case. | Bug fixes. |

| 2.90 | Updated internal API | Bug fixes. |

| 2.80 | Added hyperbus support to CAT1C family. | Code Enhancements. |

| 2.70 | Added enhancements related to CAT1D family. | Support added for sending dummy cycles using RWDS line, selecting DLL speed options and RX Capture mode. |

| Added API Cy_SMIF_Reset_Memory, updated APIs Cy_SMIF_MemInit, | Support added for SMIF octal DDR with RWDS and bug fixes. | |

| 2.60 | Modified private APIs | MISRA-10.6 violation and Bug fixes. |

| Added new API Cy_SMIF_SetSelectedDelayTapSel and Cy_SMIF_GetSelectedDelayTapSel. | Support for CAT1D devices. | |

| Modified Cy_SMIF_MemWrite and Cy_SMIF_MemDeInit APIs. | Code Enhancement. | |

| 2.50 | Future functionality support for Hyperbus devices. | Code Enhancements. |

| 2.40 | Enhanced Cy_SMIF_MemEraseSector to compute sector boundary for erase operation and Minor Bug fixes. | Code Enhancements. |

| Added new API Cy_SMIF_MemCmdPowerDown and Cy_SMIF_MemCmdReleasePowerDown. | Reduce power consumption. | |

| Added new API Cy_SMIF_DeviceTransfer_SetMergeTimeout and Cy_SMIF_DeviceTransfer_ClearMergeTimeout. | Allow user to configure merge timeout. | |

| Removed Bridge API support. | Removed feature not supported in existing devices. | |

| 2.30 | Octal SDR and DDR support using SFDP mode. | Octal device support. |

| Move SFDP related functionality to cy_smif_sfdp.c. | Code Enhancements. | |

| Added support for new product families | Support for CAT1B and CAT1C devices. | |

| Added new API's: Cy_SMIF_MemInitSfdpMode() Cy_SMIF_SetCryptoIV() Cy_SMIF_SetCryptoKey() Cy_SMIF_ConvertSlaveSlotToIndex() Cy_SMIF_SetCryptoEnable() Cy_SMIF_SetCryptoDisable() Cy_SMIF_SetReadyPollingDelay() Following macros renamed: CY_SMIF_WRITE_STATUS_REG2_CMD to CY_SMIF_WRITE_STATUS_REG2_T1_CMD. | Support for SFDP 1.0 devices. | |

| Added new API's for CAT1D devices Cy_SMIF_SetRxCaptureMode() Cy_SMIF_Bridge_Enable() Cy_SMIF_Bridge_SetPortPriority() Cy_SMIF_Bridge_SetSimpleRemapRegion() Cy_SMIF_Bridge_SetInterleavingRemapRegion() Cy_SMIF_MemOctalEnable() | Support for CAT1D devices. | |

| 2.20 | Bug fixes in Cy_SMIF_MemEraseSector for Hybrid memory configuration. Updated Cy_SMIF_MemIsReady to use Cy_SysLib_Rtos_Delay and Cy_SysLib_Rtos_DelayUs. | Code enhancement. |

| 2.10 | New silicon family support. | Added extended API for DDR support. |

| 2.0 | Reworked the Cy_SMIF_MemRead and Cy_SMIF_MemWrite functions to use polling instead of interrupts. | Extend the usability of these functions. |

| Reworked the length-parameter check in the Cy_SMIF_MemEraseSector function. The Erase operation is not performed and CY_SMIF_SUCCESS is no longer returned when the sectors are not aligned. | Fix the user error-handling of the length parameter. | |

| Fixed the address-parameter check in the Cy_SMIF_MemLocateHybridRegion function. CY_SMIF_SUCCESS or CY_SMIF_NOT_HYBRID_MEM is no longer returned when the address exceeds the memory size. | Address a defect. | |

| Fixed MISRA 2012 violations. | MISRA 2012 compliance. | |

| 1.50.1 | Minor documentation updates. | Documentation improvement. |

| 1.50 | Added a new function: Cy_SMIF_MemLocateHybridRegion. Added a new structure cy_stc_smif_hybrid_region_info_t. Updated the Cy_SMIF_MemEraseSector and Cy_SMIF_MemCmdSectorErase functions. Updated the Cy_SMIF_MemSfdpDetect function. Updated the cy_stc_smif_mem_device_cfg_t structure. | Support for memories with hybrid regions. |

| 1.40.1 | The Cy_SMIF_MemInit is changed. | Corrected a false assertion during initialization in SFDP mode. |

| Minor documentation updates. | ||

| 1.40 | The following functions are renamed: Cy_SMIF_GetTxfrStatus into Cy_SMIF_GetTransferStatus; Cy_SMIF_Memslot_Init into Cy_SMIF_MemInit; Cy_SMIF_Memslot_DeInit into Cy_SMIF_MemDeInit; Cy_SMIF_Memslot_CmdWriteEnable into Cy_SMIF_MemCmdWriteEnable; Cy_SMIF_Memslot_CmdWriteDisable into Cy_SMIF_MemCmdWriteDisable; Cy_SMIF_Memslot_IsBusy into Cy_SMIF_MemIsBusy; Cy_SMIF_Memslot_QuadEnable into Cy_SMIF_MemQuadEnable; Cy_SMIF_Memslot_CmdReadSts into Cy_SMIF_MemCmdReadStatus; Cy_SMIF_Memslot_CmdWriteSts into Cy_SMIF_MemCmdWriteStatus; Cy_SMIF_Memslot_CmdChipErase into Cy_SMIF_MemCmdChipErase; Cy_SMIF_Memslot_CmdSectorErase into Cy_SMIF_MemCmdSectorErase; Cy_SMIF_Memslot_SfdpDetect into Cy_SMIF_MemSfdpDetect; Cy_SMIF_Memslot_CmdProgram into Cy_SMIF_MemCmdProgram; Cy_SMIF_Memslot_CmdRead into Cy_SMIF_MemCmdRead. The following ENUMa are renamed: CY_SMIF_SEND_CMPLT into CY_SMIF_SEND_COMPLETE; CY_SMIF_REC_CMPLT into CY_SMIF_RX_COMPLETE; CY_SMIF_REC_BUSY into CY_SMIF_RX_BUSY; CY_SMIF_SEL_INV_INTERNAL_CLK into CY_SMIF_SEL_INVERTED_INTERNAL_CLK; CY_SMIF_SEL_INV_FEEDBACK_CLK into CY_SMIF_SEL_INVERTED_FEEDBACK_CLK; cy_en_smif_cache_en_t into cy_en_smif_cache_t. The following MACROs are renamed: CY_SMIF_FLAG_WR_EN into CY_SMIF_FLAG_WRITE_ENABLE; CY_SMIF_FLAG_CRYPTO_EN into CY_SMIF_FLAG_CRYPTO_ENABLE; CY_SMIF_SFDP_SING_BYTE_00 into CY_SMIF_SFDP_SIGNATURE_BYTE_00; CY_SMIF_SFDP_SING_BYTE_01 into CY_SMIF_SFDP_SIGNATURE_BYTE_01; CY_SMIF_SFDP_SING_BYTE_02 into CY_SMIF_SFDP_SIGNATURE_BYTE_02; CY_SMIF_SFDP_SING_BYTE_03 into CY_SMIF_SFDP_SIGNATURE_BYTE_03; CY_SMIF_WR_STS_REG1_CMD into CY_SMIF_WRITE_STATUS_REG1_CMD; CY_SMIF_WR_DISABLE_CMD into CY_SMIF_WRITE_DISABLE_CMD; CY_SMIF_RD_STS_REG1_CMD into CY_SMIF_READ_STATUS_REG1_CMD; CY_SMIF_WR_ENABLE_CMD into CY_SMIF_WRITE_ENABLE_CMD; CY_SMIF_RD_STS_REG2_T1_CMD into CY_SMIF_READ_STATUS_REG2_T1_CMD; CY_SMIF_WR_STS_REG2_CMD into CY_SMIF_WRITE_STATUS_REG2_CMD; CY_SMIF_RD_STS_REG2_T2_CMD into CY_SMIF_READ_STATUS_REG2_T2_CMD; CY_SMIF_QE_BIT_STS_REG2_T1 into CY_SMIF_QE_BIT_STATUS_REG2_T1; CY_SMIF_STS_REG_BUSY_MASK into CY_SMIF_STATUS_REG_BUSY_MASK. | Documentation improvement. |

| Updated the description of the Cy_SMIF_MemInit() function. Updated the Cy_SMIF_Encrypt() function usage example. | ||

| The type of arguments that are not modified by the functions are set to const. | Usability improvement. | |

| The Cy_SMIF_MemSfdpDetect() function is updated to support new commands for 4 bytes addressing. | Memory devices with new 4 byte addressing commands support. | |

| Added the blocking functions which take care of the busy-status check of the memory: | Added new high-level blocking functions. | |

| 1.30 | The CY_SMIF_CMD_FIFO_WR_RX_COUNT_Msk value is changed to 0x0000FFFFUL. | Driver maintenance. |

| Added the check of the size parameter in the Cy_SMIF_TransmitData() function. | ||

| Added conditional check for presence of the SMIF hardware IP. | ||

| Fixed the wrong erase command in the SFDP protocol for devices with Erase Type 3. | ||

| Updated the General Description section with minor changes. Updated the ordering of the parameters descriptions for some functions. Added the text saying that the Cy_SMIF_MemInit() function is applicable to use the external memory as memory-mapped to PSoC (XIP mode). Added the snippet for the Cy_SMIF_Encrypt() function to show how to use this function. Added below the picture in the Low-Level Functions section the sequence of PDL functions required in a Read or Write transaction. Added the text below the picture about the address. Updated DUMMY COUNT in this picture. Added checking of the size parameter in the Cy_SMIF_TransmitData() function. | Documentation improvement. | |

| 1.20.1 | Added upper limit to size parameter in several functions. | Documentation improvement. |

| 1.20 | Flattened the organization of the driver source code into the single source directory and the single include directory. | Driver library directory-structure simplification. |

| Added a new return status and transfer width option for the case when the memory command is not supported. | Improved the memory command structure usability. | |

| Added register access layer. Use register access macros instead of direct register access using dereferenced pointers. | Makes register access device-independent, so that the PDL does not need to be recompiled for each supported part number. | |

| 1.11 | Fixed internal function that writes to the SMIF FIFO | The write function stuck in the loop when write speed in external memory is significantly lower than PSoC CPU core speed and write transfer is not finished during the single function call. |

| Added optional mode part to the program command flow | Extend usability of program command | |

| 1.10.1 | Added Low Power Callback section | Documentation update and clarification |

| 1.10 | Fix write to external memory from CM0+ core. Add checks of API input parameters. Minor documentation updates | |

| 1.0 | Initial version |

API Reference | |

| Macros | |

| Functions | |

| Data Structures | |

| Enumerated Types | |