This driver provides the user an easy method for accessing standard Host Controller Interface (HCI) registers and provides some simple functionality on top of the HCI for reading and writing data to an SD card, eMMc card or a SDIO device.

The functions and other declarations used in this driver are in cy_sd_host.h. You can include cy_pdl.h to get access to all functions and declarations in the PDL.

Features:

Unsupported Features:

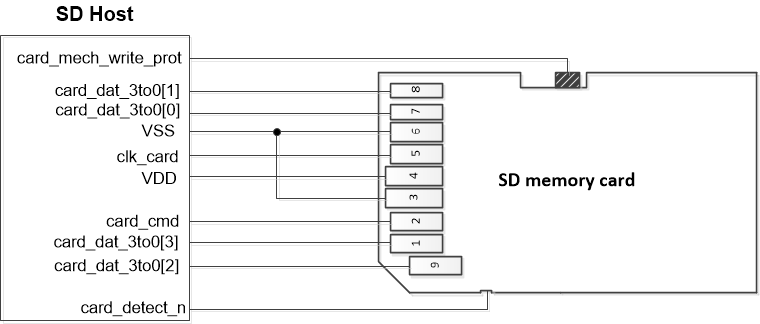

The SD, eMMC, and SDIO cards have the similar physical interface: clock, command line, and data lines. The SD card is removable and requires the SD card connector to connect to the PSoC device. This connector also has the card_mech_write_prot switch for mechanical write protection and the card_detect_n switch for card detection. The eMMC card also has DAT4-DAT7 pins for 8-bit mode and the EMMC_RESET pin.

The driver has a low-level and high-level APIs. The low-level functions provide an easy method to read and write registers. Also, these functions allow valid interaction with an SD Card, eMMC card, and SDIO card. The high-level functions provide an easy mechanism to enumerate a device, read, write, and erase data. They are RTOS-friendly. When starting a command, these functions do not wait until the command completes. The interrupt and flags are used to check when the transfer completes. This allows to put RTOS delays in the user code.

The SD Host driver configuration can be divided to a number of sequential steps listed below:

Enable the SDHC block calling Cy_SD_Host_Enable.

Only dedicated SD Host pins can be used for SD Host operation. The HSIOM register must be configured to connect the block to the pins. Also, the SD Host pins must be configured in Strong Drive, Input buffer on:

The SD Host is sourced from the CLK_HF clock. The clock must be set to 100 MHz:

The user can set up the interrupt for SD Host operation. The user is responsible for writing its own Interrupt handler. The Interrupt must be called in the interrupt handler for the selected SDHC instance. Also this interrupt must be enabled in the NVIC otherwise it will not work. It is the user's responsibility to clear the normal and error interrupt statuses. The interrupt statuses can be read using Cy_SD_Host_GetNormalInterruptStatus and Cy_SD_Host_GetErrorInterruptStatus. To clear the interrupt statuses, use Cy_SD_Host_ClearNormalInterruptStatus and Cy_SD_Host_ClearErrorInterruptStatus.

To set up the SD Host driver, provide the configuration parameters in the cy_stc_sd_host_init_config_t structure. Set the emmc parameter to true for the eMMC-device, otherwise set it to false. Set dmaType if DMA mode is used for read/write operations. The other parameters are optional for operation. To initialize the driver, call the Cy_SD_Host_Init function providing a pointer to the filled cy_stc_sd_host_init_config_t structure and allocated cy_stc_sd_host_context_t.

The SD, eMMC or SDIO card can be configured using the Cy_SD_Host_InitCard function as a pointer to the filled cy_stc_sd_host_sd_card_config_t structure and allocated cy_stc_sd_host_context_t.

Finally, enable the card operation calling Cy_SD_Host_InitCard.

The master API is divided into two categories: High-Level and Low-Level. Therefore, there are two methods for initiating SD card transactions using either Low-Level or High-Level API.

Call Cy_SD_Host_Read or Cy_SD_Host_Write to communicate with the SD memory device. These functions do not block in DMA mode and only start a transaction. After a transaction starts, the user should check the further data-transaction complete event. The example below shows sending and reading data in DMA mode.

Call Cy_SD_Host_InitDataTransfer to initialize the SD block for a data transfer. It does not start a transfer. To start a transfer call Cy_SD_Host_SendCommand after calling this function. If DMA is not used for Data transfer then the buffer needs to be filled with data first if this is a write. Wait the transfer complete event. ADMA3 mode requires calling Cy_SD_Host_InitDataTransfer to initialize the DMA transaction. The ADMA3 mode example is shown below.

eMMC cards use the same API for writing and reading data. Additionally, eMMC requires configuring GPIO pins for DAT signals in 8-bit mode and card_emmc_reset_n pin if needed. The emmc member of cy_stc_sd_host_init_config_t structure must be set to "true".

Cy_SD_Host_InitCard() initializes all types of cards and automatically detects the card type: SD, SDIO or Combo card. SDIO cards have their input-output (I/O) functions that can be controlled using the GPIO driver. Combo Cards can use both I/O and memory API.

The SD Host does not operate in Hibernate and Deep Sleep modes but it can automatically continue write/read operation after restoring from Deep Sleep mode. SD CLK must be disabled before going to Deep Sleep mode and can be enabled after wake up from Deep Sleep mode. To reduce the power consumption in Active mode, the user can stop the clock of the SD bus but the following interrupts can be allowed: Card Insert, Card Removal and SDIO Interrupt.

SD card removal or insertion can be detected by calling Cy_SD_Host_GetNormalInterruptStatus which returns the card removal or card insertion events (CY_SD_HOST_CARD_REMOVAL or CY_SD_HOST_CARD_INSERTION bits). These events should be reset using Cy_SD_Host_ClearNormalInterruptStatus when they occur. When the card is removed, the SDHC block disables the CMD/DAT output. It is recommended to set DAT pins to the Digital High-Z (CY_GPIO_DM_HIGHZ) drive mode when card removal is detected. This can be doing using the GPIO driver. When the card is inserted, the SDHC block automatically disables the card power and clock. After card insertion, the user should set the DAT pins drive mode back to Strong Drive, Input buffer on (CY_GPIO_DM_STRONG), and then call Cy_SD_Host_InitCard.

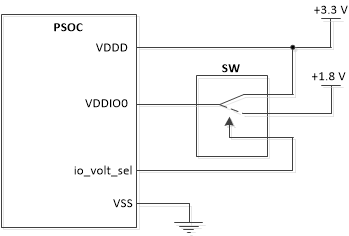

When lowVoltageSignaling is true, the SD Host driver sets UHS-I mode during the card initialization. The SD Host driver always starts talking to the card at 3.3V and then later switches to 1.8V. There is no internal regulator in the PSoC 6 to change SD signals from 3.3V to 1.8V. Thus, an external regulator is needed for the VDDIO of the PSoC device to provide the ability to go from 3.3V to 1.8V. The SD Host driver sets the io_volt_sel pin to high which is used to control the external regulator.

Refer to the appropriate device technical reference manual (TRM) for a detailed description of the registers.

| MISRA Rule | Rule Class (Required/Advisory) | Rule Description | Description of Deviation(s) |

|---|---|---|---|

| 11.4 | A | A cast should not be performed between a pointer to object type and a different pointer to object type. | The function Cy_SD_Host_DeepSleepCallback is the callback of the cy_en_syspm_status_t type. The cast operation safety in these functions becomes the user's responsibility because pointers are initialized when the callback is registered in the SysPm driver. |

| 20.3 | R | The validity of values passed to library functions shall be checked. | This violation is not caused by code changes, i.e. is not a regression. |

| Version | Changes | Reason for Change |

|---|---|---|

| 1.50.1 | Minor documentation updates. | Documentation enhancement. |

| 1.50 | The default value of the SD-clock rump-up time during a wakeup from Deep Sleep is reduced to 1 us, for details, see Cy_SD_Host_DeepSleepCallback description. | Optimization for cases of specific wakeup timing requirements. |

| 1.40 | Added a possibility to customize the SD-clock rump-up time during a wakeup from Deep Sleep, for details, see Cy_SD_Host_DeepSleepCallback description. | Workaround for cases of specific wakeup timing requirements. |

| 1.30 | The internal function implementation is changed. | Code efficiency enhancement, minor defect fixing. |

| 1.20 | Added the Cy_SD_Host_DeepSleepCallback() function. | Driver maintenance. |

| Fixed the Cy_SD_Host_GetCsd() function behaviour. Now the cy_stc_sd_host_context_t::maxSectorNum is being updated correctly | Defect fixing. | |

| 1.10.1 | Documentation of the MISRA rule violation. | MISRA compliance. |

| 1.10 | The PLL and CLK disable sequence in Cy_SD_Host_DisableSdClk() is changed to disable CLK first. The Low-Power Support section is updated with additional information about disabling CLK. The context initialization in Cy_SD_Host_Init() is corrected. Updated the Write/Read sequence in Cy_SD_Host_Read() and functions for non DMA mode. | Defect fixing. |

| 1.0 | The initial version. |

API Reference | |

| Macros | |

| Functions | |

| Data Structures | |

| Enumerated Types | |