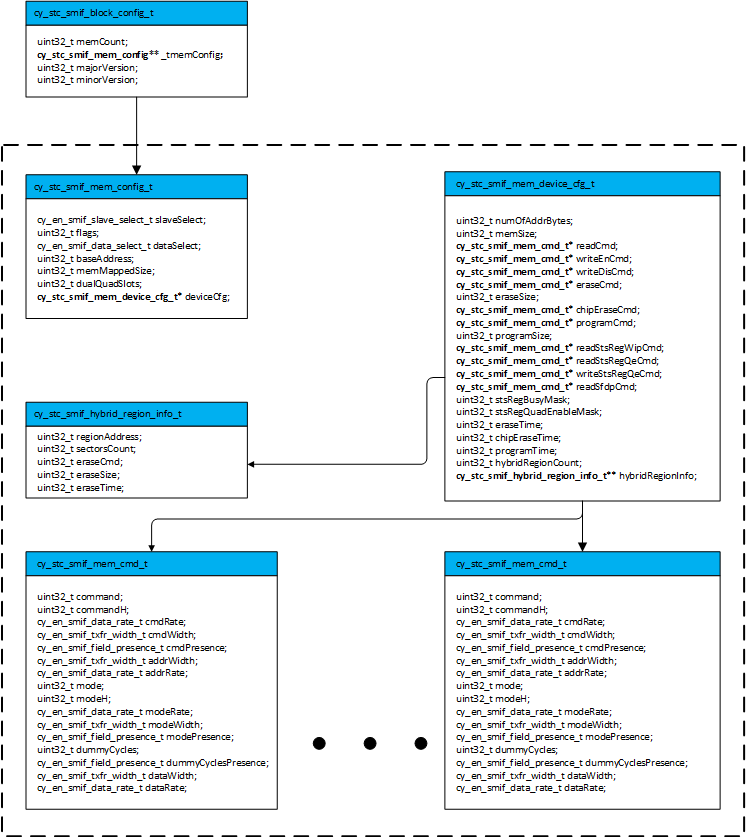

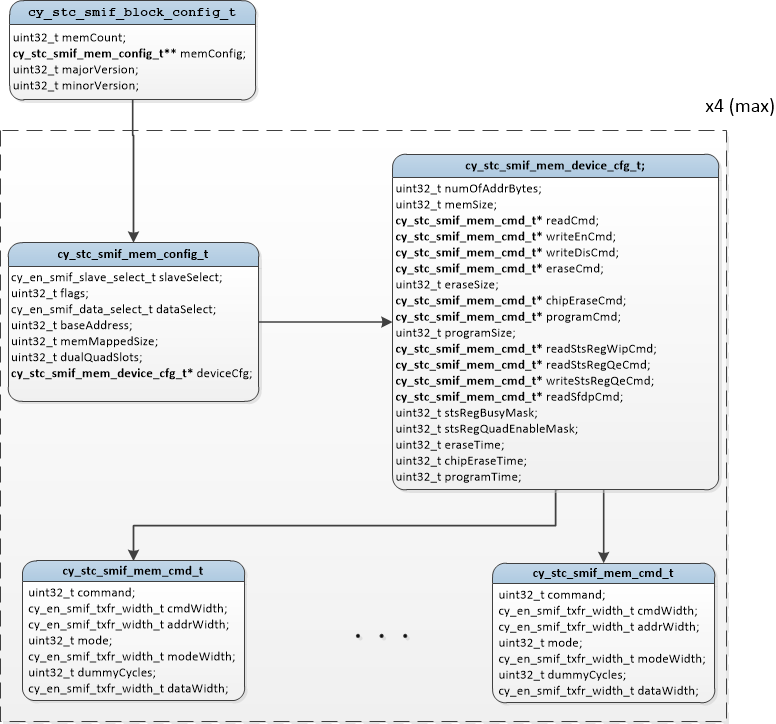

General hierarchy of memory structures are:

Top structure is cy_stc_smif_block_config_t, which could have links up to 4 cy_stc_smif_mem_config_t which describes each connected to the SMIF external memory.

Data Structures | |

| struct | cy_stc_smif_mem_cmd_t |

| This command structure is used to store the Read/Write command configuration. More... | |

| struct | cy_stc_smif_hybrid_region_info_t |

| This structure specifies data used for memory with hybrid sectors. More... | |

| struct | cy_stc_smif_octal_ddr_en_seq_t |

| This structure specifies data used for memory with hybrid sectors. More... | |

| struct | cy_stc_smif_hbmem_device_config_t |

| HyperBus device configuration structure. More... | |

| struct | cy_stc_smif_mem_device_cfg_t |

| This configuration structure of the SMIF memory device is used to store device-specific parameters. More... | |

| struct | cy_stc_smif_mem_config_t |

| This SMIF memory configuration structure is used to store the memory configuration for the memory mode of operation. More... | |

| struct | cy_stc_smif_block_config_t |

| This SMIF memory configuration structure is used to store the memory configuration for the memory mode of operation. More... | |

| struct cy_stc_smif_mem_cmd_t |

| Data Fields | ||

|---|---|---|

| uint32_t | command |

The 8-bit command. This value is 0xFFFFFFFF when there is no command present |

| cy_en_smif_txfr_width_t | cmdWidth | The width of the command transfer. |

| cy_en_smif_txfr_width_t | addrWidth | The width of the address transfer. |

| uint32_t | mode |

The 8-bit mode byte. This value is 0xFFFFFFFF when there is no mode present |

| cy_en_smif_txfr_width_t | modeWidth | The width of the mode transfer. |

| uint32_t | dummyCycles |

The number of the dummy cycles. A zero value suggests no dummy cycles |

| cy_en_smif_txfr_width_t | dataWidth | The width of the data transfer. |

| cy_en_smif_data_rate_t | dataRate | The Data rate of data. |

| cy_en_smif_field_presence_t | dummyCyclesPresence | This specifies the presence of the dummy field. |

| cy_en_smif_field_presence_t | modePresence | This specifies the presence of the mode field. |

| uint32_t | modeH |

The 8-bit command. This value is 0x0 when there is no higher byte mode present |

| cy_en_smif_data_rate_t | modeRate | The Data rate of mode. |

| cy_en_smif_data_rate_t | addrRate | The Data rate of address. |

| cy_en_smif_field_presence_t | cmdPresence | This specifies the presence of the command field. |

| uint32_t | commandH |

The 8-bit command. This value is 0x0 when there is no higher byte command present |

| cy_en_smif_data_rate_t | cmdRate | The Data rate of command. |

| struct cy_stc_smif_hybrid_region_info_t |

| struct cy_stc_smif_octal_ddr_en_seq_t |

| Data Fields | ||

|---|---|---|

| uint8_t | cmdSeq1Len | This specifies command sequence 1 length. |

| uint8_t | cmdSeq2Len | This specifies command sequence 2 length. |

| uint8_t | cmdSeq1[CY_SMIF_SFDP_ODDR_CMD_SEQ_MAX_LEN] | This specifies command sequence 1. |

| uint8_t | cmdSeq2[CY_SMIF_SFDP_ODDR_CMD_SEQ_MAX_LEN] | This specifies command sequence 2. |

| struct cy_stc_smif_hbmem_device_config_t |

| Data Fields | ||

|---|---|---|

| cy_en_smif_hb_rd_cmd_t | xipReadCmd | read command value cy_en_smif_hb_rd_cmd_t |

| cy_en_smif_hb_wt_cmd_t | xipWriteCmd | write command value cy_en_smif_hb_rd_cmd_t |

| cy_en_smif_hb_dev_type_t | hbDevType | hyper bus device type cy_en_smif_hb_dev_type_t |

| cy_en_device_size_t | memSize |

The memory size: For densities of 2 gigabits or less - the size in bytes; For densities 4 gigabits and above - bit-31 is set to 1b to define that this memory is 4 gigabits and above; and other 30:0 bits define N where the density is computed as 2^N bytes. For example, 0x80000021 corresponds to 2^30 = 1 gigabyte. |

| uint32_t | dummyCycles | dummy Cycles based on Frequency of operation |

| struct cy_stc_smif_mem_device_cfg_t |

| Data Fields | ||

|---|---|---|

| uint32_t | numOfAddrBytes | This specifies the number of address bytes used by the memory slave device, valid values 1-4. |

| uint32_t | memSize |

The memory size: For densities of 2 gigabits or less - the size in bytes; For densities 4 gigabits and above - bit-31 is set to 1b to define that this memory is 4 gigabits and above; and other 30:0 bits define N where the density is computed as 2^N bytes. For example, 0x80000021 corresponds to 2^30 = 1 gigabyte. |

| cy_stc_smif_mem_cmd_t * | readCmd | This specifies the Read command. |

| cy_stc_smif_mem_cmd_t * | writeEnCmd | This specifies the Write Enable command. |

| cy_stc_smif_mem_cmd_t * | writeDisCmd | This specifies the Write Disable command. |

| cy_stc_smif_mem_cmd_t * | eraseCmd | This specifies the Erase command. |

| uint32_t | eraseSize | This specifies the sector size of each Erase. |

| cy_stc_smif_mem_cmd_t * | chipEraseCmd | This specifies the Chip Erase command. |

| cy_stc_smif_mem_cmd_t * | programCmd | This specifies the Program command. |

| uint32_t | programSize | This specifies the page size for programming. |

| cy_stc_smif_mem_cmd_t * | readStsRegWipCmd |

This specifies the command to read the WIP-containing status register |

| cy_stc_smif_mem_cmd_t * | readStsRegQeCmd | This specifies the command to read the QE-containing status register. |

| cy_stc_smif_mem_cmd_t * | writeStsRegQeCmd | This specifies the command to write into the QE-containing status register. |

| cy_stc_smif_mem_cmd_t * | readSfdpCmd | This specifies the read SFDP command. |

| uint32_t | stsRegBusyMask | The Busy mask for the status registers. |

| uint32_t | stsRegQuadEnableMask | The QE mask for the status registers. |

| uint32_t | eraseTime | Max time for erase type 1 cycle time in ms. |

| uint32_t | chipEraseTime | Max time for chip erase cycle time in ms. |

| uint32_t | programTime | Max time for page program cycle time in us. |

| uint32_t | hybridRegionCount | This specifies the number of regions for memory with hybrid sectors. |

| cy_stc_smif_hybrid_region_info_t ** | hybridRegionInfo | This specifies data for memory with hybrid sectors. |

| cy_stc_smif_mem_cmd_t * | readLatencyCmd | This specifies the command to read variable latency cycles configuration register. |

| cy_stc_smif_mem_cmd_t * | writeLatencyCmd | This specifies the command to write variable latency cycles configuration register. |

| uint32_t | latencyCyclesRegAddr | This specifies the address for variable latency cycle address. |

| uint32_t | latencyCyclesMask | This specifies variable latency cycles Mask. |

| cy_stc_smif_octal_ddr_en_seq_t * | octalDDREnableSeq | This specifies data for memory with hybrid sectors. |

| cy_stc_smif_mem_cmd_t * | readStsRegOeCmd | This specifies the command to read the OE-containing status register. |

| cy_stc_smif_mem_cmd_t * | writeStsRegOeCmd | This specifies the command to write into the OE-containing status register. |

| uint32_t | stsRegOctalEnableMask | The QE mask for the status registers. |

| uint32_t | octalEnableRegAddr | Octal enable register address. |

| cy_en_smif_interface_freq_t | freq_of_operation | Frequency of operation used in Octal mode. |

| struct cy_stc_smif_mem_config_t |

| Data Fields | ||

|---|---|---|

| cy_en_smif_slave_select_t | slaveSelect | Determines the slave select where the memory device is placed. |

| uint32_t | flags | Determines if the device is memory-mapped, enables the Autodetect using the SFDP, enables the write capability, or enables the crypto support for this memory slave. |

| cy_en_smif_data_select_t | dataSelect | The data-line selection options for a slave device. |

| uint32_t | baseAddress |

The base address the memory slave is mapped to in the PSoC memory map. This address must be a multiple of the SMIF XIP memory size/capacity. The SMIF XIP memory region should NOT overlap with other memory regions (with exception to dual quad mode). Valid when the memory-mapped mode is enabled. |

| uint32_t | memMappedSize |

The size/capacity allocated in the PSoC memory map for the memory slave device. The capacity is allocated from the base address. The capacity must be a power of 2 and greater or equal than 64 KB. Valid when memory-mapped mode is enabled |

| uint32_t | dualQuadSlots |

Defines if this memory device is one of the devices in the dual quad SPI configuration. Equals the sum of the slave-slot numbers. |

| cy_stc_smif_mem_device_cfg_t * | deviceCfg | The configuration of the device. |

| cy_en_smif_merge_timeout_t | mergeTimeout |

Continuous transfer merge timeout. After this period the memory device is deselected. A later transfer, even from a continuous address, starts with the overhead phases (command, address, mode, dummy cycles). |

| cy_stc_smif_hbmem_device_config_t * | hbdeviceCfg | The configuration of the hyperbus device. |

| struct cy_stc_smif_block_config_t |

| Data Fields | ||

|---|---|---|

| uint32_t | memCount |

The number of SMIF memory defined |

| cy_stc_smif_mem_config_t ** | memConfig | The pointer to the array of the memory configuration structures of size Memory_count. |

| uint32_t | majorVersion | The version of the SMIF driver. |

| uint32_t | minorVersion | The version of the SMIF Driver. |

Specifies top 8 bit of read/write sequence (bit 47 ~ bit 40).

only top 3 bits have meaning bit 47: Identifies the transaction as a Read or Write. R/W#=1 indicates a Read operation and R/W#=0 indicates a Write operation. bit 46: Indicates whether the Read or Write operation accesses the memory or register spaces. bit 45: Indicates whether the burst will be continuous or wrapped. Burst Type=0 indicates Wrapped Burst, Burst Type=1 indicates Continuous Burst. bit 46 is always 0, since this drive assumes accessing memory space in XIP mode

| Enumerator | |

|---|---|

| CY_SMIF_HB_READ_WRAPPED_BURST | bit 47 = 1: read, bit 45 = 0: wrapped burst |

| CY_SMIF_HB_READ_CONTINUOUS_BURST | bit 47 = 1: read, bit 45 = 1: continuous burst |

| enum cy_en_device_size_t |

The size of the device region specified by DEVICE_MASK register.

| enum en_cy_sub_page_nr_t |

Specifies the number of sub pages per page.

Specifies the size of the XIP device address in Bytes.

| enum cy_en_hb_target_t |