This driver provides API functions to configure the PTComp subsystem of the Autonomous Analog.

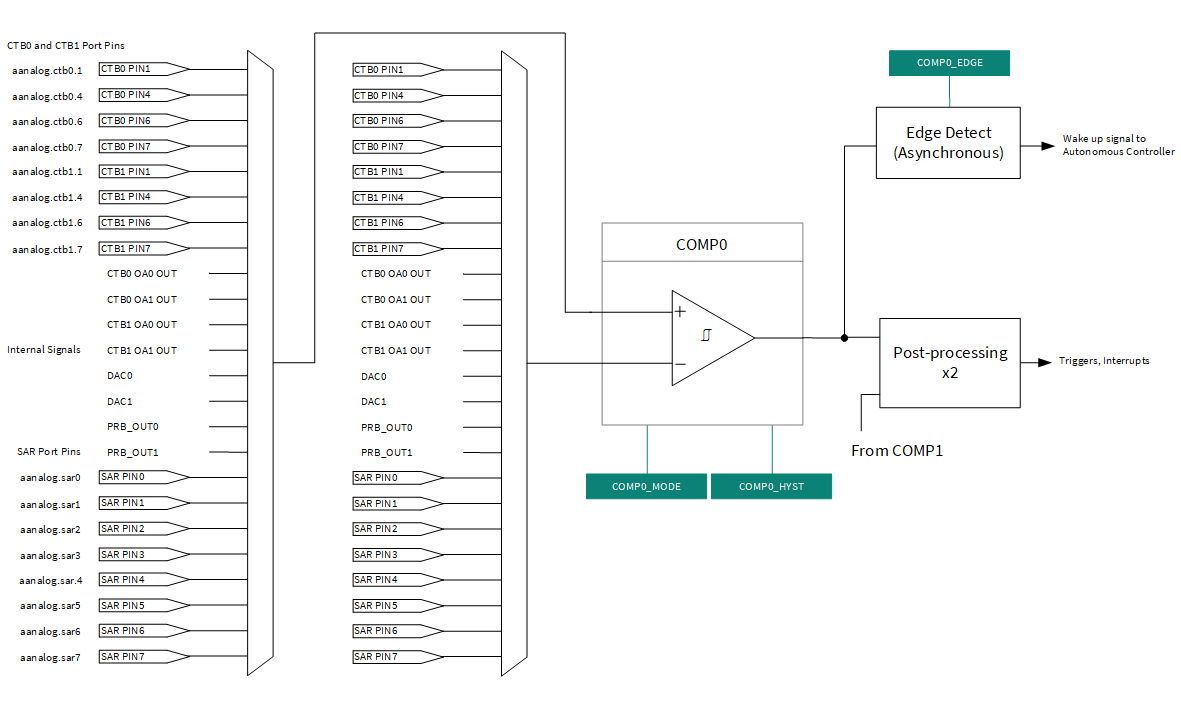

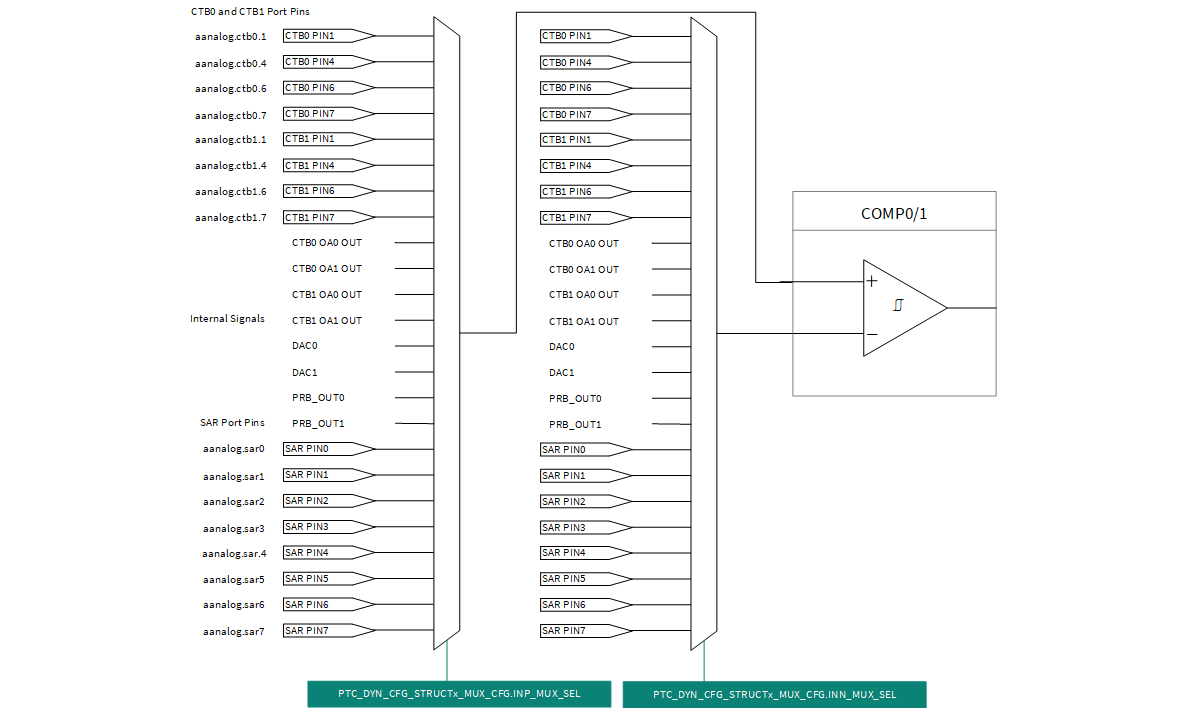

The PTComp block provides a pair of comparators that are used to compare the voltage on one input to the reference on another input.

For more information on the PTComp, refer to the device Architecture Technical Reference Manual (TRM).

For the exact location of the pins, see the device datasheet.

The static configuration contains application-specific settings intended to remain static for any PTComp application. The Autonomous Controller (AC) will NOT change the static configuration during operation.

The static configuration of the Comp includes:

For configuration settings, see cy_stc_autanalog_ptcomp_comp_sta_t structure.

The dynamic configuration structure includes the Comp settings, which can be modified by the Autonomous Controller (AC) during operation.

The Autonomous Controller is able to modify the following characteristics of the PTComp in runtime per settings provided in the State Transition Table:

For configuration settings, see cy_stc_autanalog_ptcomp_comp_dyn_t and cy_stc_autanalog_stt_ptcomp_t structures.

The PTComp contains two post-processing blocks that can be used to measure time between events and/or count events. The Comp state (level) or rising/falling change can be used as an input event for post-processing.

The PTComp post-processing can operate in the following modes (cy_stc_autanalog_ptcomp_comp_pp_t::cntMode):

The post-processing result of each Comp can be combined together using the dual-input look-up table block. This block implements a set of Boolean functions cy_stc_autanalog_ptcomp_comp_pp_t::dataFunction and allows a common functional logic to be defined for a pair of Comps.

The PTComp is clocked from the SRSS peripheral clock (Clk_HF9, up to 80MHz, refer to General Configuration Considerations) in chip Active mode using Peri 0 Clock Group 2 8-bit divider in the clock chain.

Or from the local Low Power Oscillator (LPOSC, 4096kHz, refer to cy_en_autanalog_timer_clk_src_t) in chip Deep Sleep mode. The clock value can be adjusted using dedicated divider cy_stc_autanalog_ptcomp_comp_sta_t::lpDivPtcomp, which divides the incoming clock in chip Deep Sleep mode.

The following internal events of the PTComp can be configured to generate an interrupt or trigger or used as the STT event in the Autonomous Analog (refer to cy_en_autanalog_ac_out_trigger_mask_t and cy_en_autanalog_stt_ac_condition_t):

API Reference | |

| Macros | |

| Functions | |

| Data Structures | |

| Enumerated Types | |