The CSDIDAC middleware is the IDAC solution that uses the CSD HW block. Any GPIO that can be connected to AMUX-A/B (refer to the particular device datasheet for information) can be an CSDIDAC output under software control. The CSD HW block is mainly used to implement the touch sense applications and proximity sensors (refer to the CapSense Middleware API Reference Guide), but can also be used to implement the IDAC, which is especially useful for the devices that do not include another hardware option to implement IDAC.

Features:

| LSB Index | LSB | Available Current Range |

|---|---|---|

| 0 | 37.5 nA | 0 to 4762.5 nA |

| 1 | 75.0 nA | 0 to 9525.0 nA |

| 2 | 0.3 uA | 0 to 38.1 uA |

| 3 | 0.6 uA | 0 to 76.2 uA |

| 4 | 2.4 uA | 0 to 304.8 uA |

| 5 | 4.8 uA | 0 to 609.6 uA |

Include cy_csdidac.h to get access to all functions and other declarations in this library. The Quick Start Guide is offered in this API Reference Guide.

Refer to the Supported Software and Tools for the compatibility information.

Refer to the Changelog for the differences between the middleware versions. Changelog also describes the impact of changes to your code.

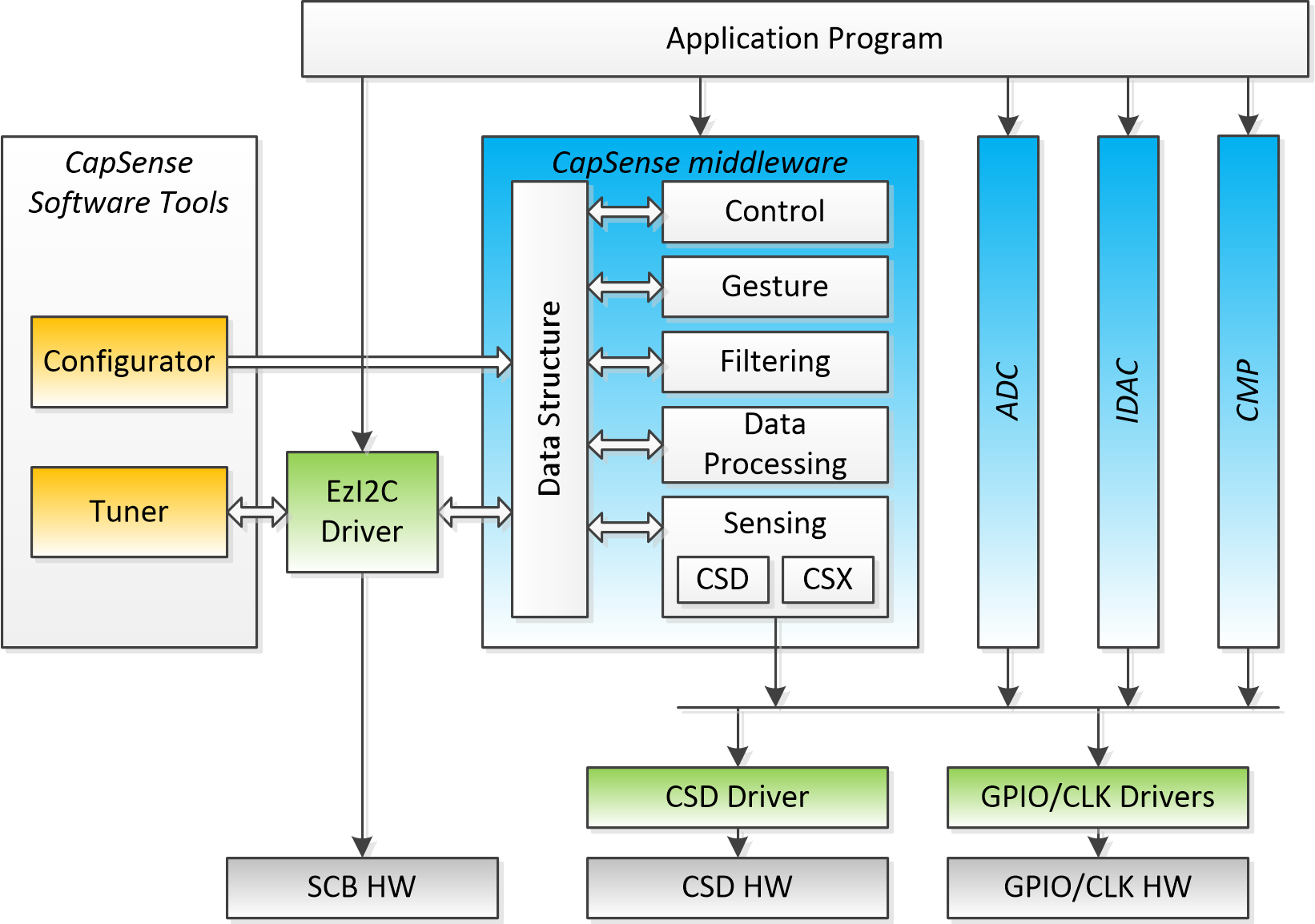

The CSD HW block enables the multiple sensing capabilities on PSoC devices including the self-cap and mutual-cap capacitive touch sensing solution, 10-bit ADC, IDAC, and Comparator. The CSD driver is a low-level peripheral driver, a wrapper to manage access to the CSD HW block. Any middleware access to the CSD HW block is through the CSD Driver.

The CSD HW block can support only one function at a time. However, all supported functionality (like CapSense, CSDADC, CSDIDAC, etc.) can be time-multiplexed in a design. I.e. you can save the existing state of the CapSense middleware, restore the state of the CSDIDAC middleware, perform DAC operations, and then switch back to the CapSense functionality. For more details and code examples, refer to the description of the Cy_CSDIDAC_Save() and Cy_CSDIDAC_Restore() functions.

This section describes only the CSDIDAC middleware. Refer to the corresponding sections for documentation of other middleware supported by the CSD HW block. The CSDIDAC library is designed to be used with the CSD driver. The application program does not need to interact with the CSD driver and/or other drivers such as GPIO or SysClk directly. All of that is configured and managed by the middleware.

The Cy_CSDIDAC API is described in the following sections:

The CSDIDAC middleware can be used in various Development Environments such as ModusToolbox, MBED, etc. Refer to the Supported Software and Tools. The quickest way to get started is using the Code Examples. The continually expanding portfolio of the code examples is available at the Cypress Semiconductor website and on GitHub.

This quick start guide assumes that the environment is configured to use the PSoC 6 Peripheral Driver Library(psoc6pdl) for development and the PSoC 6 Peripheral Driver Library(psoc6pdl) is included in the project.

The steps required to set up the CSDIDAC and get the desired current:

The CSDIDAC middleware operates on the top of the CSD Driver included in the PSoC 6 Peripheral Driver Library (psoc6pdl). Refer to the "CSD(CapSense Sigma Delta)" section of the PSoC 6 Peripheral Driver Library (psoc6pdl) API Reference Manual. This section guides how to set up the CSDIDAC middleware for the operation with the following parameters:

There are two methods for the CSDIDAC Middleware configuration:

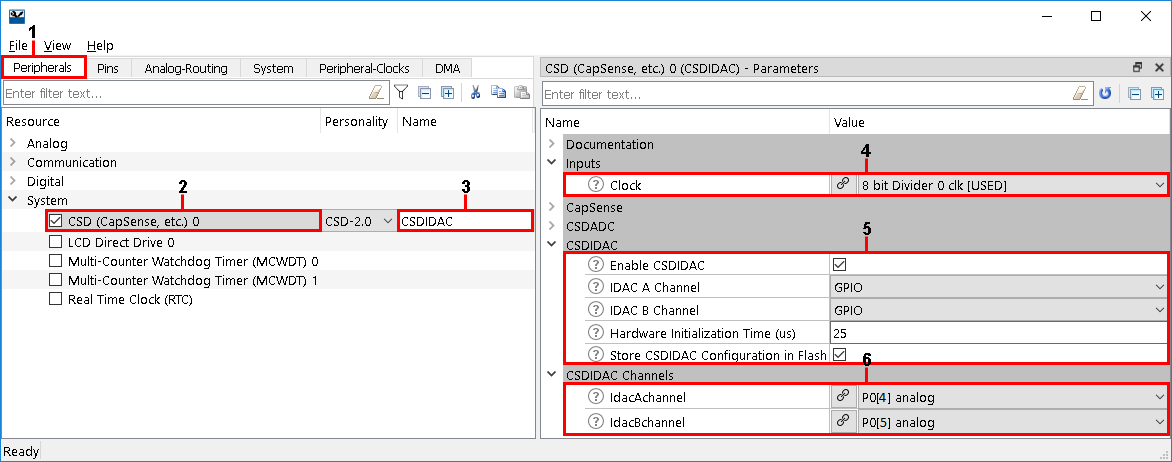

Generation of the initialization code using the ModusToolbox Device Configurator Tool which is part of the ModusToolbox, greatly simplifies the PSoC configuration. The ModusToolbox Device Configurator Tool provides the user interface to set up and automatically generate the initialization code (including analog routing) and configuration structures.

Manual implementation of the initialization code (including analog routing) and configuration structures is recommended for expert Users only. This will include the code for the following settings which in case of the Device Configurator usage are generated automatically based upon the settings entered in its UI:

The steps required to generate the initialization code using the ModusToolbox Device Configurator Tool :

Now, all required CSDIDAC initialization code and configuration prerequisites will be generated:

The generated code will be available under the GeneratedSource folder.

Refer to Quick Start Guide section for the application layer code required to set up the CSDIDAC and to get the desired current on the assigned pin.

The steps required to implement the initialization code manually:

Set the configuration of the HSIOM_AMUX_SPLIT_CTL switches to route signal from CSD HW block to the pins configured as the CSDIDAC output channels.

The AMUX bus has segments that are separated with the HSIOM_AMUX_SPLIT_CTL switches. The code below closes the AMUX_SPLIT_CTL switches, which route the IDAC output signal from the CSD block to the pin. In this example, IDAC output channels are assigned to the P0[4] and P[5] pins. The AMUX_SPLIT_CTL[5] and AMUX_SPLIT_CTL[6] switches must be closed in the PSoC6 device. The P0[4] and P[5] pins in the PSoC4 device belong to the AMUX bus segment, which is connected to the CSD block directly. In this case, the AMUX_SPLIT_CTL switches are not closed. Refer to the Technical Reference Manual (TRM) for more information regarding the analog interconnection. See the code example below and refer to the main() routine code snippet in Quick Start Guide

Refer to Quick Start Guide section for the application layer code required to set up the CSDIDAC and to get the desired current on the assigned pin.

This section provides descriptions and links to additional documentation for some specific CSDIDAC use cases.

The CSD HW block and CSDIDAC middleware can operate in CPU active and CPU sleep power modes. It is also possible to switch between low power and ultra low power system modes. In System Deep Sleep and Hibernate power modes, the CSD HW block is powered off and CSDIDAC operations are not performed. Before entering CPU / System Deep Sleep, disable CSDIDAC output current generation. If output currents are not disabled, a CPU Deep Sleep transition will fail. When the device wakes up from CPU / System Deep Sleep, the CSD HW block resumes operation without the need for re-initialization and the CSDIDAC operations can be continued with configuration that was set before a CPU / System Deep Sleep transition. When the device wakes up from Hibernate power mode, the CSD HW block does not retain the configuration and CSDIDAC requires re-initialization.

Refer to the Cy_CSDIDAC_DeepSleepCallback() function description and to the SysPm (System Power Management) driver documentation for the low power design considerations.

Sleep mode

The CSD HW block can operate in CPU sleep mode. The user can start CSDIDAC and move CPU into sleep mode to reduce power consumption. After wake-up CPU from sleep, the user can perform other operations, e.g. disable IDACs. Then, the user configures the CSDIDAC middleware as described in Configuration Considerations, and updates the main() routine with the following code:

Deep Sleep mode

To use the CSDIDAC middleware in CPU / System Deep Sleep mode, the user configures a wake-up source (e.g. a pin, WDT, LPC or another entities, that are active in CPU / System Deep Sleep mode), configures the CSDIDAC middleware as described in Configuration Considerations, configures CSDIDAC and other drivers' and middleware's (if present) Deep Sleep Callback structures, registers callbacks, and updates the main() routine with the following code:

Refer to the CapSense Middleware API Reference Guide for implementation of the time-multiplexing operation by using common CSD HW block.

This version of the CSDIDAC Middleware was validated for compatibility with the following Software and Tools:

| Software and Tools | Version |

|---|---|

| ModusToolbox Software Environment | 2.1 |

| - ModusToolbox Device Configurator | 2.1 |

| - ModusToolbox CSD Personality for PSoC4 devices in Device Configurator | 1.0 |

| - ModusToolbox CSD Personality for PSoC6 devices in Device Configurator | 2.0 |

| PSoC4 Peripheral Driver Library (PDL) | 1.0.0 |

| PSoC6 Peripheral Driver Library (PDL) | 1.5.0 |

| GCC Compiler | 7.2.1 |

| IAR Compiler | 8.32 |

| Arm Compiler 6 | 6.11 |

| MBED OS (only for PSoC6) | 5.15.1 |

| FreeRTOS | 10.0.1 |

Consult Changelog to learn about the design impact of the newer version. Set up your environment in accordance with Supported Software and Tools. You might need to re-generate the configuration structures for either the device initialization code or the middleware initialization code.

Ensure:

The Cy_CSDIDAC library has the following specific deviations:

| MISRA Rule | Rule Class (Required/Advisory) | Rule Description | Description of Deviation(s) |

|---|---|---|---|

| 11.4 | A | Do not perform a conversion between the pointer to an object and an integer type. | Such a conversion is performed with CSDIDAC context in the DeepSleepCallback() function. This case is verified on correct operation. |

| 1.2 | R | Constant: De-reference of the NULL pointer. | These violations are reported as a result of using offset macros of the CSD Driver with corresponding documented violation 20.6. Refer to the CSD Driver API Reference Guide. |

| 20.3 |

| Version | Changes | Reason for Change |

|---|---|---|

| 2.10 | Added the support of PSoC 4 CapSense Forth Generation devices | Devices support |

| Minor documentation update | Documentation cleanup | |

| 2.0 | The joining two IDAC channels option is added to increase the maximum CSDIDAC output current | Feature enchancement |

| The cy_stc_csdidac_config_t structure is changed: the periClk field replaced with cpuClk, busOnlyA and busOnlyB fields replaced with configA and configB fields respectively, the field order is changed. The cy_en_csdidac_channel_config_t enumeration type is added. | User experience improvement | |

| The CY_CSDIDAC_HW_FAILURE and the CY_CSDIDAC_BAD_CONFIGURATION return status cases are added to the cy_en_csdidac_status_t enumeration type | User experience improvement | |

| The CY_CSDIDAC_AB choosing case for both IDACs is added to the cy_en_csdidac_choice_t enumeration type | Feature enchancement | |

| The CSDIDAC MW sources are enclosed with the conditional compilation to ensure a successful compilation for non-CapSense-capable devices | Compilation for non-CapSense-capable devices | |

| 1.0 | The initial version |

Important information about the CapSense-technology overview, appropriate device for the design, CapSense system and sensor design guidelines, different interfaces and tuning guidelines necessary for a successful design of a CapSense system is available in the Getting Started with CapSense document and the product-specific CapSense design guide. It is highly recommended to start with these documents. They can be found at www.cypress.com.

For more information, refer to the following documents: