Ethernet is a well-defined industry specification.

Ethernet MAC module transmits and receives IEEE 802.3 frames by connecting with the PHY device using MII/RMII/GMII or RGMII interface. Ethernet MAC also supports 10/100/1000 Transfer rates and IEEE 1588 time stamp feature. Infineon uses a third-party Ethernet MAC IP from Cadence GEM_GXL, which is a Gigabit Ethernet MAC.

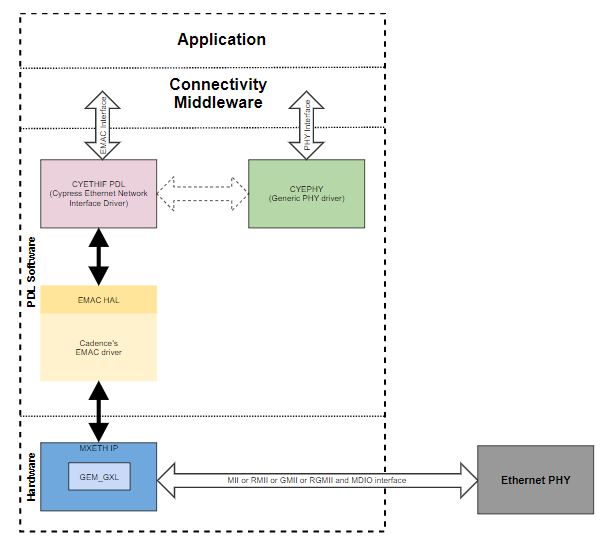

Below block diagram shows the hardware and software partition inside the MCU. Ethernet MAC IP hardware directly interface with external ethernet PHY via MII or RMII or GMII or RGMII interface and MDIO interface is for configuring the Ethernet PHY chip/device. The software section consists of three major layers Ethernet PDL (Peripheral Driver Library), Connectivity Middleware, and Applications. Ethernet PDL implements low level driver for Ethernet MAC and a generic driver for the external Ethernet PHY chips.

The ETHIF driver is wrapper around Cadence's EMAC core driver. This is a network interface driver to Cadence core EMAC driver. It provides APIs to communicate with Ethernet IP. The PHY driver also uses this driver to communicate with PHY chip (via application). This driver has internal buffer management, handling callbacks from Cadence EMAC during transport, etc.

The functions and other declarations used in this driver are in cy_ethif.h. You can include cy_pdl.h (ModusToolbox only) to get access to all functions and declarations in the PDL.

Refer to the technical reference manual (TRM) and the device datasheet.

The Ethernet driver has no specific deviations

| Version | Changes | Reason for Change |

|---|---|---|

| 1.50 | Added new Cy_ETHIF_GetPrivateData API getter. | Code enhancement. |

| 1.40 | Added initialization checks for Cy_ETHIF_Get1588TimerValue and Cy_ETHIF_Set1588TimerValue functions, added new cy_en_ethif_status_t CY_ETHIF_NOT_INITIALIZED return status. | Defect fix. |

| 1.30 | Added an internal low power callback. | Code enhancement. |

| 1.20 | Documentation update and updated pre-processor check for CM55. | Code enhancement. |

| 1.10.1 | Build warning fixes due to redefinitions. | Bug fixes. |

| 1.10 | Updated an internal API and fixed MISRA 2012 violations. | MISRA 2012 compliance and code enhancement. |

| 1.0 | Initial version |

API Reference | |

| Macros | |

| Functions | |

| Data Structures | |

| Enumerated Types | |