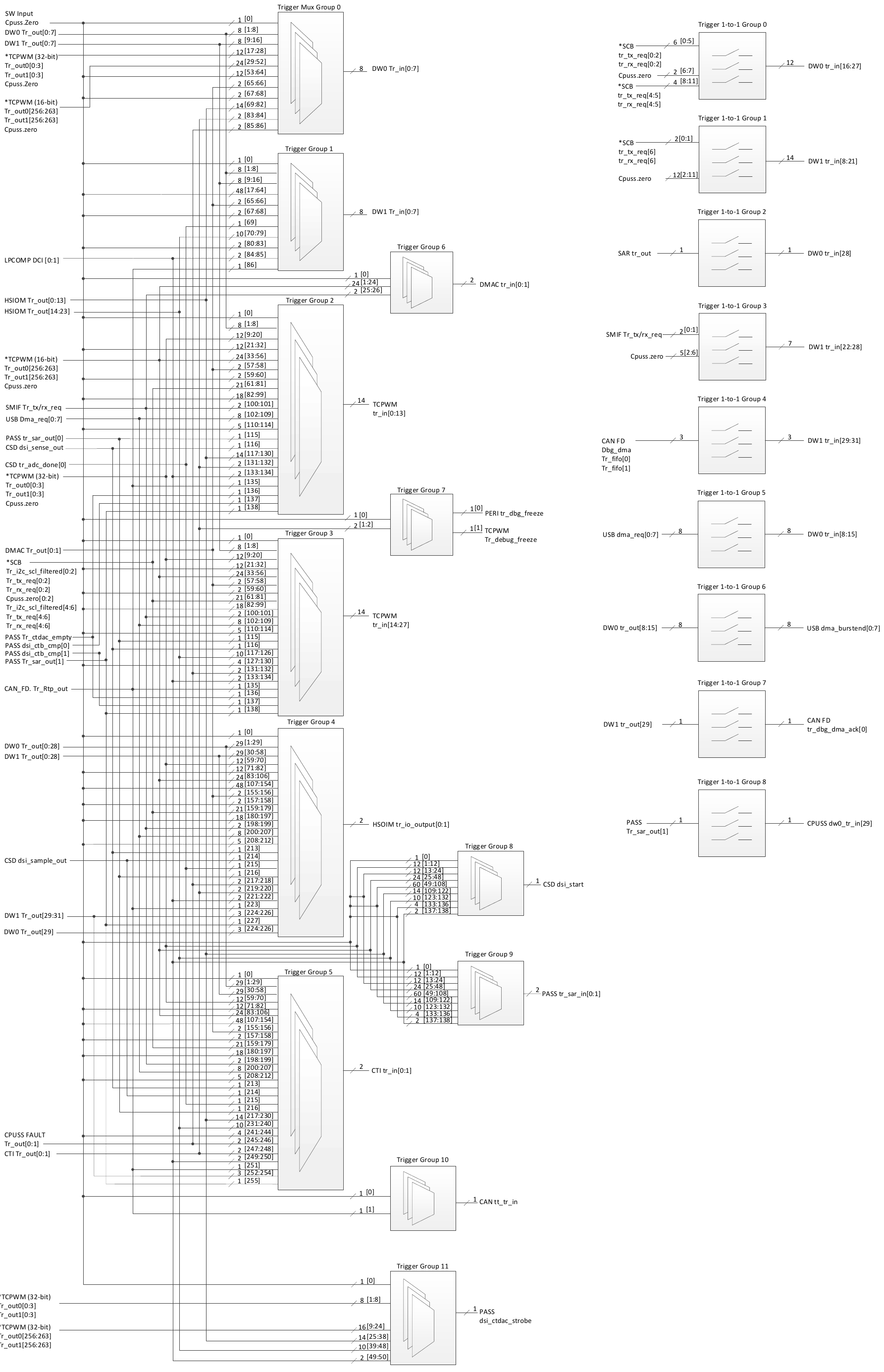

Trigger connections for psoc6_04.

PSoC™ 6S4 Triggers:

Macros | |

| #define | CYHAL_TRIGGER_CPUSS_ZERO (CYHAL_TRIGGER_CPUSS_ZERO_LEVEL) |

| Deprecated defines for signals that can be either level or edge. More... | |

| #define | CYHAL_TRIGGER_CSD_DSI_SENSE_OUT (CYHAL_TRIGGER_CSD_DSI_SENSE_OUT_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_CSD_TR_ADC_DONE (CYHAL_TRIGGER_CSD_TR_ADC_DONE_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PASS_DSI_CTB_CMP0 (CYHAL_TRIGGER_PASS_DSI_CTB_CMP0_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PASS_DSI_CTB_CMP1 (CYHAL_TRIGGER_PASS_DSI_CTB_CMP1_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT0 (CYHAL_TRIGGER_PERI_TR_IO_INPUT0_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT1 (CYHAL_TRIGGER_PERI_TR_IO_INPUT1_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT2 (CYHAL_TRIGGER_PERI_TR_IO_INPUT2_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT3 (CYHAL_TRIGGER_PERI_TR_IO_INPUT3_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT4 (CYHAL_TRIGGER_PERI_TR_IO_INPUT4_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT5 (CYHAL_TRIGGER_PERI_TR_IO_INPUT5_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT6 (CYHAL_TRIGGER_PERI_TR_IO_INPUT6_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT7 (CYHAL_TRIGGER_PERI_TR_IO_INPUT7_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT8 (CYHAL_TRIGGER_PERI_TR_IO_INPUT8_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT9 (CYHAL_TRIGGER_PERI_TR_IO_INPUT9_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT10 (CYHAL_TRIGGER_PERI_TR_IO_INPUT10_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT11 (CYHAL_TRIGGER_PERI_TR_IO_INPUT11_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT12 (CYHAL_TRIGGER_PERI_TR_IO_INPUT12_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT13 (CYHAL_TRIGGER_PERI_TR_IO_INPUT13_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT14 (CYHAL_TRIGGER_PERI_TR_IO_INPUT14_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT15 (CYHAL_TRIGGER_PERI_TR_IO_INPUT15_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT16 (CYHAL_TRIGGER_PERI_TR_IO_INPUT16_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT17 (CYHAL_TRIGGER_PERI_TR_IO_INPUT17_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT18 (CYHAL_TRIGGER_PERI_TR_IO_INPUT18_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT19 (CYHAL_TRIGGER_PERI_TR_IO_INPUT19_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT20 (CYHAL_TRIGGER_PERI_TR_IO_INPUT20_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT21 (CYHAL_TRIGGER_PERI_TR_IO_INPUT21_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT22 (CYHAL_TRIGGER_PERI_TR_IO_INPUT22_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_PERI_TR_IO_INPUT23 (CYHAL_TRIGGER_PERI_TR_IO_INPUT23_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT00 (CYHAL_TRIGGER_TCPWM0_TR_OUT00_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT01 (CYHAL_TRIGGER_TCPWM0_TR_OUT01_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT02 (CYHAL_TRIGGER_TCPWM0_TR_OUT02_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT03 (CYHAL_TRIGGER_TCPWM0_TR_OUT03_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0256 (CYHAL_TRIGGER_TCPWM0_TR_OUT0256_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0257 (CYHAL_TRIGGER_TCPWM0_TR_OUT0257_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0258 (CYHAL_TRIGGER_TCPWM0_TR_OUT0258_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0259 (CYHAL_TRIGGER_TCPWM0_TR_OUT0259_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0260 (CYHAL_TRIGGER_TCPWM0_TR_OUT0260_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0261 (CYHAL_TRIGGER_TCPWM0_TR_OUT0261_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0262 (CYHAL_TRIGGER_TCPWM0_TR_OUT0262_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT0263 (CYHAL_TRIGGER_TCPWM0_TR_OUT0263_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT10 (CYHAL_TRIGGER_TCPWM0_TR_OUT10_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT11 (CYHAL_TRIGGER_TCPWM0_TR_OUT11_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT12 (CYHAL_TRIGGER_TCPWM0_TR_OUT12_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT13 (CYHAL_TRIGGER_TCPWM0_TR_OUT13_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1256 (CYHAL_TRIGGER_TCPWM0_TR_OUT1256_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1257 (CYHAL_TRIGGER_TCPWM0_TR_OUT1257_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1258 (CYHAL_TRIGGER_TCPWM0_TR_OUT1258_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1259 (CYHAL_TRIGGER_TCPWM0_TR_OUT1259_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1260 (CYHAL_TRIGGER_TCPWM0_TR_OUT1260_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1261 (CYHAL_TRIGGER_TCPWM0_TR_OUT1261_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1262 (CYHAL_TRIGGER_TCPWM0_TR_OUT1262_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

| #define | CYHAL_TRIGGER_TCPWM0_TR_OUT1263 (CYHAL_TRIGGER_TCPWM0_TR_OUT1263_LEVEL) |

| Legacy define. Instead, use the explicit _LEVEL or _EDGE version. | |

Typedefs | |

| typedef cyhal_trigger_source_psoc6_04_t | cyhal_source_t |

| Typedef from device family specific trigger source to generic trigger source. | |

| typedef cyhal_trigger_dest_psoc6_04_t | cyhal_dest_t |

| Typedef from device family specific trigger dest to generic trigger dest. | |

Enumerations | |

| enum | cyhal_trigger_source_psoc6_04_t { CYHAL_TRIGGER_CPUSS_ZERO_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_ZERO, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_ZERO_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_ZERO, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_CANFD0_TR_DBG_DMA_REQ0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CANFD0_TR_DBG_DMA_REQ0, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_CANFD0_TR_FIFO00 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CANFD0_TR_FIFO00, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_CANFD0_TR_FIFO10 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CANFD0_TR_FIFO10, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_CANFD0_TR_TMP_RTP_OUT0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CANFD0_TR_TMP_RTP_OUT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_CTI_TR_OUT0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_CTI_TR_OUT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_CTI_TR_OUT1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_CTI_TR_OUT1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DMAC_TR_OUT0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DMAC_TR_OUT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DMAC_TR_OUT1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DMAC_TR_OUT1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT2 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT2, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT3 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT3, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT4 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT4, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT5 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT5, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT6 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT6, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT7 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT7, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT8 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT8, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT9 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT9, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT10 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT10, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT11 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT11, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT12 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT12, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT13 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT13, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT14 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT14, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT15 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT15, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT16 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT16, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT17 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT17, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT18 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT18, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT19 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT19, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT20 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT20, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT21 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT21, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT22 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT22, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT23 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT23, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT24 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT24, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT25 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT25, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT26 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT26, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT27 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT27, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT28 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT28, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW0_TR_OUT29 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW0_TR_OUT29, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT2 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT2, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT3 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT3, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT4 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT4, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT5 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT5, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT6 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT6, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT7 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT7, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT8 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT8, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT9 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT9, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT10 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT10, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT11 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT11, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT12 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT12, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT13 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT13, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT14 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT14, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT15 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT15, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT16 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT16, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT17 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT17, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT18 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT18, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT19 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT19, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT20 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT20, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT21 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT21, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT22 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT22, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT23 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT23, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT24 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT24, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT25 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT25, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT26 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT26, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT27 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT27, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT28 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT28, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT29 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT29, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT30 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT30, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_DW1_TR_OUT31 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_DW1_TR_OUT31, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_TR_FAULT0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_TR_FAULT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CPUSS_TR_FAULT1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CPUSS_TR_FAULT1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CSD_DSI_SAMPLE_OUT = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CSD_DSI_SAMPLE_OUT, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CSD_DSI_SENSE_OUT_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CSD_DSI_SENSE_OUT, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CSD_DSI_SENSE_OUT_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CSD_DSI_SENSE_OUT, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_CSD_TR_ADC_DONE_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CSD_TR_ADC_DONE, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_CSD_TR_ADC_DONE_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_CSD_TR_ADC_DONE, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_LPCOMP_DSI_COMP0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_LPCOMP_DSI_COMP0, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_LPCOMP_DSI_COMP1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_LPCOMP_DSI_COMP1, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PASS_DSI_CTB_CMP0_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PASS_DSI_CTB_CMP0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PASS_DSI_CTB_CMP0_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PASS_DSI_CTB_CMP0, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PASS_DSI_CTB_CMP1_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PASS_DSI_CTB_CMP1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PASS_DSI_CTB_CMP1_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PASS_DSI_CTB_CMP1, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PASS_TR_CTDAC_EMPTY = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PASS_TR_CTDAC_EMPTY, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PASS_TR_SAR_OUT0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PASS_TR_SAR_OUT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PASS_TR_SAR_OUT1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PASS_TR_SAR_OUT1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT0_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT0_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT0, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT1_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT1_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT1, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT2_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT2, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT2_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT2, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT3_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT3, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT3_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT3, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT4_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT4, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT4_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT4, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT5_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT5, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT5_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT5, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT6_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT6, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT6_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT6, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT7_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT7, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT7_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT7, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT8_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT8, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT8_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT8, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT9_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT9, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT9_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT9, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT10_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT10, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT10_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT10, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT11_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT11, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT11_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT11, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT12_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT12, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT12_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT12, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT13_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT13, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT13_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT13, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT14_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT14, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT14_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT14, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT15_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT15, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT15_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT15, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT16_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT16, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT16_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT16, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT17_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT17, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT17_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT17, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT18_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT18, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT18_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT18, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT19_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT19, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT19_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT19, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT20_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT20, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT20_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT20, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT21_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT21, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT21_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT21, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT22_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT22, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT22_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT22, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_PERI_TR_IO_INPUT23_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT23, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_PERI_TR_IO_INPUT23_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_PERI_TR_IO_INPUT23, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB0_TR_I2C_SCL_FILTERED = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB0_TR_I2C_SCL_FILTERED, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB1_TR_I2C_SCL_FILTERED = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB1_TR_I2C_SCL_FILTERED, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB2_TR_I2C_SCL_FILTERED = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB2_TR_I2C_SCL_FILTERED, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB4_TR_I2C_SCL_FILTERED = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB4_TR_I2C_SCL_FILTERED, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB5_TR_I2C_SCL_FILTERED = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB5_TR_I2C_SCL_FILTERED, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB6_TR_I2C_SCL_FILTERED = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB6_TR_I2C_SCL_FILTERED, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB0_TR_RX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB0_TR_RX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB1_TR_RX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB1_TR_RX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB2_TR_RX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB2_TR_RX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB4_TR_RX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB4_TR_RX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB5_TR_RX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB5_TR_RX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB6_TR_RX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB6_TR_RX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB0_TR_TX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB0_TR_TX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB1_TR_TX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB1_TR_TX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB2_TR_TX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB2_TR_TX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB4_TR_TX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB4_TR_TX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB5_TR_TX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB5_TR_TX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SCB6_TR_TX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SCB6_TR_TX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SMIF_TR_RX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SMIF_TR_RX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_SMIF_TR_TX_REQ = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_SMIF_TR_TX_REQ, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT00_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT00, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT00_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT00, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT01_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT01, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT01_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT01, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT02_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT02, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT02_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT02, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT03_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT03, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT03_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT03, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0256_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0256, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0256_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0256, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0257_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0257, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0257_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0257, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0258_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0258, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0258_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0258, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0259_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0259, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0259_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0259, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0260_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0260, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0260_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0260, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0261_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0261, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0261_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0261, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0262_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0262, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0262_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0262, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT0263_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0263, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT0263_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT0263, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT10_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT10, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT10_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT10, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT11_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT11, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT11_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT11, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT12_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT12, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT12_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT12, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT13_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT13, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT13_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT13, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1256_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1256, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1256_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1256, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1257_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1257, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1257_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1257, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1258_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1258, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1258_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1258, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1259_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1259, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1259_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1259, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1260_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1260, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1260_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1260, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1261_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1261, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1261_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1261, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1262_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1262, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1262_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1262, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_TCPWM0_TR_OUT1263_EDGE = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1263, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_TCPWM0_TR_OUT1263_LEVEL = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_TCPWM0_TR_OUT1263, CYHAL_SIGNAL_TYPE_LEVEL) , CYHAL_TRIGGER_USB_DMA_REQ0 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ0, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_USB_DMA_REQ1 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ1, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_USB_DMA_REQ2 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ2, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_USB_DMA_REQ3 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ3, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_USB_DMA_REQ4 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ4, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_USB_DMA_REQ5 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ5, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_USB_DMA_REQ6 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ6, CYHAL_SIGNAL_TYPE_EDGE) , CYHAL_TRIGGER_USB_DMA_REQ7 = _CYHAL_TRIGGER_CREATE_SOURCE(_CYHAL_TRIGGER_USB_DMA_REQ7, CYHAL_SIGNAL_TYPE_EDGE) } |

| Name of each input trigger. More... | |

| enum | cyhal_trigger_dest_psoc6_04_t { CYHAL_TRIGGER_CANFD0_TR_DBG_DMA_ACK0 = 0 , CYHAL_TRIGGER_CANFD0_TR_EVT_SWT_IN0 = 1 , CYHAL_TRIGGER_CPUSS_CTI_TR_IN0 = 2 , CYHAL_TRIGGER_CPUSS_CTI_TR_IN1 = 3 , CYHAL_TRIGGER_CPUSS_DMAC_TR_IN0 = 4 , CYHAL_TRIGGER_CPUSS_DMAC_TR_IN1 = 5 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN0 = 6 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN1 = 7 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN2 = 8 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN3 = 9 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN4 = 10 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN5 = 11 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN6 = 12 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN7 = 13 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN8 = 14 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN9 = 15 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN10 = 16 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN11 = 17 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN12 = 18 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN13 = 19 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN14 = 20 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN15 = 21 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN16 = 22 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN17 = 23 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN18 = 24 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN19 = 25 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN20 = 26 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN21 = 27 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN22 = 28 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN23 = 29 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN24 = 30 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN25 = 31 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN26 = 32 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN27 = 33 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN28 = 34 , CYHAL_TRIGGER_CPUSS_DW0_TR_IN29 = 35 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN0 = 36 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN1 = 37 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN2 = 38 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN3 = 39 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN4 = 40 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN5 = 41 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN6 = 42 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN7 = 43 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN8 = 44 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN9 = 45 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN10 = 46 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN11 = 47 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN12 = 48 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN13 = 49 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN14 = 50 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN15 = 51 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN16 = 52 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN17 = 53 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN18 = 54 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN19 = 55 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN20 = 56 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN21 = 57 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN22 = 58 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN23 = 59 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN24 = 60 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN25 = 61 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN26 = 62 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN27 = 63 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN28 = 64 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN29 = 65 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN30 = 66 , CYHAL_TRIGGER_CPUSS_DW1_TR_IN31 = 67 , CYHAL_TRIGGER_CSD_DSI_START = 68 , CYHAL_TRIGGER_PASS_DSI_CTDAC_STROBE = 69 , CYHAL_TRIGGER_PASS_TR_SAR_IN0 = 70 , CYHAL_TRIGGER_PASS_TR_SAR_IN1 = 71 , CYHAL_TRIGGER_PERI_TR_DBG_FREEZE = 72 , CYHAL_TRIGGER_PERI_TR_IO_OUTPUT0 = 73 , CYHAL_TRIGGER_PERI_TR_IO_OUTPUT1 = 74 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN0 = 75 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN1 = 76 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN2 = 77 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN3 = 78 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN4 = 79 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN5 = 80 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN6 = 81 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN7 = 82 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN8 = 83 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN9 = 84 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN10 = 85 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN11 = 86 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN12 = 87 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN13 = 88 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN14 = 89 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN15 = 90 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN16 = 91 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN17 = 92 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN18 = 93 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN19 = 94 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN20 = 95 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN21 = 96 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN22 = 97 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN23 = 98 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN24 = 99 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN25 = 100 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN26 = 101 , CYHAL_TRIGGER_TCPWM0_TR_ALL_CNT_IN27 = 102 , CYHAL_TRIGGER_TCPWM0_TR_DEBUG_FREEZE = 103 , CYHAL_TRIGGER_USB_DMA_BURSTEND0 = 104 , CYHAL_TRIGGER_USB_DMA_BURSTEND1 = 105 , CYHAL_TRIGGER_USB_DMA_BURSTEND2 = 106 , CYHAL_TRIGGER_USB_DMA_BURSTEND3 = 107 , CYHAL_TRIGGER_USB_DMA_BURSTEND4 = 108 , CYHAL_TRIGGER_USB_DMA_BURSTEND5 = 109 , CYHAL_TRIGGER_USB_DMA_BURSTEND6 = 110 , CYHAL_TRIGGER_USB_DMA_BURSTEND7 = 111 } |

| Name of each output trigger. More... | |

| #define CYHAL_TRIGGER_CPUSS_ZERO (CYHAL_TRIGGER_CPUSS_ZERO_LEVEL) |

Deprecated defines for signals that can be either level or edge.

Legacy define. Instead, use the explicit _LEVEL or _EDGE version.

Name of each input trigger.

Name of each output trigger.