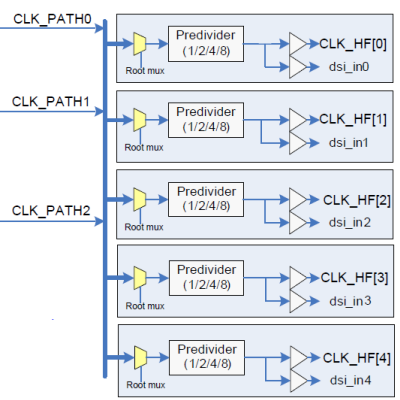

Multiple high frequency clocks (CLK_HF) are available in the device.

For example, PSoC 63 series has five high-frequency root clocks. Each CLK_HF has a particular connection and chip-specific destination on the device.

| Name | Description |

|---|---|

| CLK_HF[0] | Root clock for CPUs, PERI, and AHB infrastructure |

| CLK_HF[1] | Root clock for the PDM/PCM and I2S audio subsystem |

| CLK_HF[2] | Root clock for the Serial Memory Interface subsystem |

| CLK_HF[3] | Root clock for USB communications |

| CLK_HF[4] | Clock output on clk_ext pin (when used as an output) |

Note this is a particular example. The actual tree may vary depending on the device series. Consult the Technical Reference Manual for your device for details.

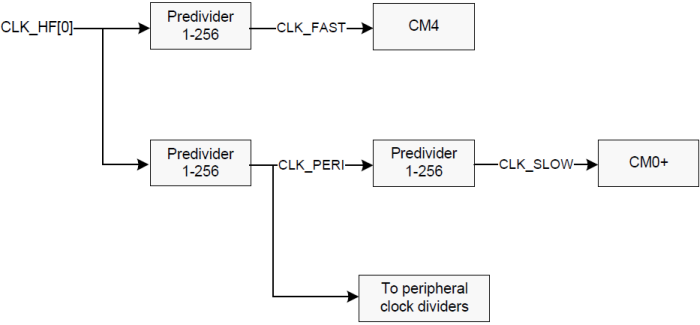

High frequency clocks are sourced by path clocks, which should be configured first. An exception to this rule is CLK_HF[0], which cannot be disabled. This divided clock drives the core processors and the peripherals in the system. In order to update its clock source, CLK_HF[0] source must be selected without disabling the clock.

API Reference | |

| Functions | |

| Enumerated Types | |