Data Structures | |

| struct | XMC_USBH0_DEVICE_t |

| struct | XMC_USBH0_pipe_t |

| struct | XMC_USBH_CAPABILITIES_t |

| struct | XMC_USBH_DRIVER_t |

| struct | XMC_USBH_DRIVER_VERSION_t |

| struct | XMC_USBH_PORT_STATE_t |

Macros | |

| #define | USB_CH_HCCHARx_DEVADDR(x) (((uint32_t) x << USB_CH_HCCHAR_DevAddr_Pos) & (uint32_t)USB_CH_HCCHAR_DevAddr_Msk) |

| #define | USB_CH_HCCHARx_EPDIR(x) (((uint32_t) x << USB_CH_HCCHAR_EPDir_Pos) & (uint32_t)USB_CH_HCCHAR_EPDir_Msk) |

| #define | USB_CH_HCCHARx_EPNUM(x) (((uint32_t) x << USB_CH_HCCHAR_EPNum_Pos) & (uint32_t)USB_CH_HCCHAR_EPNum_Msk) |

| #define | USB_CH_HCCHARx_EPTYPE(x) (((uint32_t) x << USB_CH_HCCHAR_EPType_Pos) & (uint32_t)USB_CH_HCCHAR_EPType_Msk) |

| #define | USB_CH_HCCHARx_MCEC(x) (((uint32_t) x << USB_CH_HCCHAR_MC_EC_Pos) & (uint32_t)USB_CH_HCCHAR_MC_EC_Msk) |

| #define | USB_CH_HCCHARx_MPS(x) (((uint32_t) x ) & (uint32_t)USB_CH_HCCHAR_MPS_Msk) |

| #define | USB_CH_HCFG_FSLSPCS(x) (((uint32_t) x ) & USB_HCFG_FSLSPclkSel_Msk) |

| #define | USB_CH_HCFG_FSLSSUP(x) (((uint32_t) x << USB_HCFG_FSLSSupp_Pos) & USB_HCFG_FSLSSupp_Msk) |

| #define | USB_CH_HCINTx_ALL |

| #define | USB_CH_HCINTx_ERRORS |

| #define | USB_CH_HCTSIZx_DPID(x) (((uint32_t) x << USB_CH_HCTSIZ_BUFFERMODE_Pid_Pos) & (uint32_t)USB_CH_HCTSIZ_BUFFERMODE_Pid_Msk) |

| #define | USB_CH_HCTSIZx_DPID_DATA0 (USB_CH_HCTSIZx_DPID(0U)) |

| #define | USB_CH_HCTSIZx_DPID_DATA1 (USB_CH_HCTSIZx_DPID(2U)) |

| #define | USB_CH_HCTSIZx_DPID_DATA2 (USB_CH_HCTSIZx_DPID(1U)) |

| #define | USB_CH_HCTSIZx_DPID_MDATA (USB_CH_HCTSIZx_DPID(3U)) |

| #define | USB_CH_HCTSIZx_DPID_SETUP (USB_CH_HCTSIZx_DPID(3U)) |

| #define | USB_GRXSTSR_HOSTMODE_PktSts_IN_DATA_PKT 0x2 |

| #define | USB_GRXSTSR_HOSTMODE_PktSts_IN_TRSF_CPL 0x3 |

| #define | USBH0_MAX_PIPE_NUM (14U) |

| #define | USBH_PIPE_GET_INDEX(handle) (((uint32_t)handle - (uint32_t)USB0_CH0_BASE)/(0x20U)) |

| #define | XMC_USB_DRIVE_PORT1 P3_2 |

| #define | XMC_USB_DRIVE_PORT2 P0_1 |

| #define | XMC_USBH_API_VERSION ((uint16_t)((uint16_t)XMC_LIB_MAJOR_VERSION << 8U) |XMC_LIB_MINOR_VERSION) |

| #define | XMC_USBH_CLOCK_GATING_DISABLE 0 |

| #define | XMC_USBH_CLOCK_GATING_ENABLE 1 |

| #define | XMC_USBH_DRIVER_ERROR -1 |

| #define | XMC_USBH_DRIVER_ERROR_BUSY -2 |

| #define | XMC_USBH_DRIVER_ERROR_PARAMETER -5 |

| #define | XMC_USBH_DRIVER_ERROR_SPECIFIC -6 |

| #define | XMC_USBH_DRIVER_ERROR_TIMEOUT -3 |

| #define | XMC_USBH_DRIVER_ERROR_UNSUPPORTED -4 |

| #define | XMC_USBH_DRIVER_OK 0 |

| #define | XMC_USBH_ENDPOINT_BULK 2 |

| #define | XMC_USBH_ENDPOINT_CONTROL 0 |

| #define | XMC_USBH_ENDPOINT_INTERRUPT 3 |

| #define | XMC_USBH_ENDPOINT_ISOCHRONOUS 1 |

| #define | XMC_USBH_EP_HANDLE XMC_USBH_PIPE_HANDLE |

| #define | XMC_USBH_EVENT_BUS_ERROR (1UL << 6) |

| #define | XMC_USBH_EVENT_CONNECT (1UL << 0) |

| #define | XMC_USBH_EVENT_DISCONNECT (1UL << 1) |

| #define | XMC_USBH_EVENT_HANDSHAKE_ERR (1UL << 5) |

| #define | XMC_USBH_EVENT_HANDSHAKE_MDATA (1UL << 3) |

| #define | XMC_USBH_EVENT_HANDSHAKE_NAK (1UL << 1) |

| #define | XMC_USBH_EVENT_HANDSHAKE_NYET (1UL << 2) |

| #define | XMC_USBH_EVENT_HANDSHAKE_STALL (1UL << 4) |

| #define | XMC_USBH_EVENT_OVERCURRENT (1UL << 2) |

| #define | XMC_USBH_EVENT_REMOTE_WAKEUP (1UL << 6) |

| #define | XMC_USBH_EVENT_RESET (1UL << 3) |

| #define | XMC_USBH_EVENT_RESUME (1UL << 5) |

| #define | XMC_USBH_EVENT_SUSPEND (1UL << 4) |

| #define | XMC_USBH_EVENT_TRANSFER_COMPLETE (1UL << 0) |

| #define | XMC_USBH_PACKET_CSPLIT (0x0CUL << XMC_USBH_PACKET_SPLIT_Pos) |

| #define | XMC_USBH_PACKET_DATA0 (0x01UL << XMC_USBH_PACKET_DATA_Pos) |

| #define | XMC_USBH_PACKET_DATA1 (0x02UL << XMC_USBH_PACKET_DATA_Pos) |

| #define | XMC_USBH_PACKET_DATA_Msk (0x0FUL << XMC_USBH_PACKET_DATA_Pos) |

| #define | XMC_USBH_PACKET_DATA_Pos 4 |

| #define | XMC_USBH_PACKET_IN (0x03UL << XMC_USBH_PACKET_TOKEN_Pos) |

| #define | XMC_USBH_PACKET_OUT (0x02UL << XMC_USBH_PACKET_TOKEN_Pos) |

| #define | XMC_USBH_PACKET_PING (0x04UL << XMC_USBH_PACKET_TOKEN_Pos) |

| #define | XMC_USBH_PACKET_PRE (1UL << 12) |

| #define | XMC_USBH_PACKET_SETUP (0x01UL << XMC_USBH_PACKET_TOKEN_Pos) |

| #define | XMC_USBH_PACKET_SSPLIT (0x08UL << XMC_USBH_PACKET_SPLIT_Pos) |

| #define | XMC_USBH_PACKET_SSPLIT_E (0x0AUL << XMC_USBH_PACKET_SPLIT_Pos) |

| #define | XMC_USBH_PACKET_SSPLIT_S (0x09UL << XMC_USBH_PACKET_SPLIT_Pos) |

| #define | XMC_USBH_PACKET_SSPLIT_S_E (0x0BUL << XMC_USBH_PACKET_SPLIT_Pos) |

| #define | XMC_USBH_PACKET_TOKEN_Msk (0x0FUL << XMC_USBH_PACKET_TOKEN_Pos) |

| #define | XMC_USBH_PACKET_TOKEN_Pos 0 |

| #define | XMC_USBH_SignalEndpointEvent_t XMC_USBH_SignalPipeEvent_t |

| #define | XMC_USBH_SPEED_FULL 1U |

| #define | XMC_USBH_SPEED_HIGH 2U |

| #define | XMC_USBH_SPEED_LOW 0U |

Typedefs | |

| typedef void(* | XMC_USBH_SignalPipeEvent_t) (XMC_USBH_PIPE_HANDLE pipe_hndl, uint32_t event) |

| typedef void(* | XMC_USBH_SignalPortEvent_t) (uint8_t port, uint32_t event) |

Functions | |

| uint32_t | XMC_USBH_GetInterruptStatus (void) |

| void | XMC_USBH_HandleIrq (uint32_t gintsts) |

| uint8_t | XMC_USBH_osDelay (uint32_t ms) |

| void | XMC_USBH_Select_VBUS (XMC_GPIO_PORT_t *port, uint32_t pin) |

| void | XMC_USBH_TurnOffResumeBit (void) |

The USBH is the host mode device driver for the USB0 hardware module on XMC4000 family of microcontrollers. The USB0 module can be used to establish a USB interface between outside world and XMC4000 family of controllers. The USB module includes the following features in host mode:

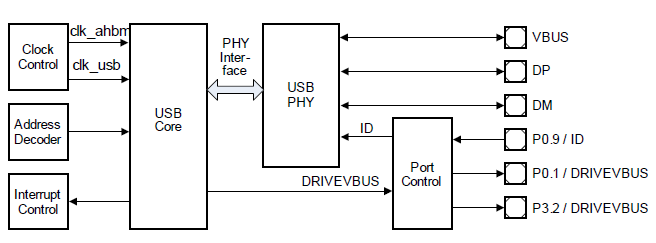

The below figure shows the overview of USB0 module in XMC4 microntroller.

The USBH device driver supports the following features:

The USBH device driver expects registration of callback functions XMC_USBH_SignalPortEvent_t and XMC_USBH_SignalPipeEvent_t to be executed when there is port event interrupt and pipe event interrupt respectively.

The USBH driver is CMSIS API compatible. Please use Driver_USBH0 to access the USBH API.

For example, to initialize the USB host controller, use Driver_USBH0.Initialize().

| #define USB_CH_HCCHARx_DEVADDR | ( | x | ) | (((uint32_t) x << USB_CH_HCCHAR_DevAddr_Pos) & (uint32_t)USB_CH_HCCHAR_DevAddr_Msk) |

Shifts the value to the position of endpoint type(EPType) in the HCCHAR register

| #define USB_CH_HCCHARx_EPDIR | ( | x | ) | (((uint32_t) x << USB_CH_HCCHAR_EPDir_Pos) & (uint32_t)USB_CH_HCCHAR_EPDir_Msk) |

Shifts the value to the position of endpoint direction(EPDir) in the HCCHAR register

| #define USB_CH_HCCHARx_EPNUM | ( | x | ) | (((uint32_t) x << USB_CH_HCCHAR_EPNum_Pos) & (uint32_t)USB_CH_HCCHAR_EPNum_Msk) |

Shifts the value to the position of endpoint number(EPNum) in the HCCHAR register

| #define USB_CH_HCCHARx_EPTYPE | ( | x | ) | (((uint32_t) x << USB_CH_HCCHAR_EPType_Pos) & (uint32_t)USB_CH_HCCHAR_EPType_Msk) |

Shifts the value to the position of endpoint type(EPType) in the HCCHAR register

| #define USB_CH_HCCHARx_MCEC | ( | x | ) | (((uint32_t) x << USB_CH_HCCHAR_MC_EC_Pos) & (uint32_t)USB_CH_HCCHAR_MC_EC_Msk) |

Shifts the value to the position of multi-count(MC_EC) field in the HCCHAR register

| #define USB_CH_HCCHARx_MPS | ( | x | ) | (((uint32_t) x ) & (uint32_t)USB_CH_HCCHAR_MPS_Msk) |

Masks maximum packet size information from the HCCHAR register value provided as input

| #define USB_CH_HCFG_FSLSPCS | ( | x | ) | (((uint32_t) x ) & USB_HCFG_FSLSPclkSel_Msk) |

Provides register value to update PHY clock selection in register HCFG

| #define USB_CH_HCFG_FSLSSUP | ( | x | ) | (((uint32_t) x << USB_HCFG_FSLSSupp_Pos) & USB_HCFG_FSLSSupp_Msk) |

Provides register value to update USB full speed related mask FLSSupp of register HCFG

| #define USB_CH_HCINTx_ALL |

Mask for selecting all channel related events

| #define USB_CH_HCINTx_ERRORS |

Mask for selecting all channel error related events

| #define USB_CH_HCTSIZx_DPID | ( | x | ) | (((uint32_t) x << USB_CH_HCTSIZ_BUFFERMODE_Pid_Pos) & (uint32_t)USB_CH_HCTSIZ_BUFFERMODE_Pid_Msk) |

Shifts the value to the position of packet ID (PID) in the HCTSIZ register

| #define USB_CH_HCTSIZx_DPID_DATA0 (USB_CH_HCTSIZx_DPID(0U)) |

Represents DATA toggle DATA0 as in HCTSIZ register

| #define USB_CH_HCTSIZx_DPID_DATA1 (USB_CH_HCTSIZx_DPID(2U)) |

Represents DATA toggle DATA1 as in HCTSIZ register

| #define USB_CH_HCTSIZx_DPID_DATA2 (USB_CH_HCTSIZx_DPID(1U)) |

Represents DATA toggle DATA2 as in HCTSIZ register

| #define USB_CH_HCTSIZx_DPID_MDATA (USB_CH_HCTSIZx_DPID(3U)) |

Represents DATA toggle MDATA as in HCTSIZ register

| #define USB_CH_HCTSIZx_DPID_SETUP (USB_CH_HCTSIZx_DPID(3U)) |

Represents SETUP token as in HCTSIZ register

| #define USB_GRXSTSR_HOSTMODE_PktSts_IN_DATA_PKT 0x2 |

Represents IN data token as in receive status pop register(GRXSTSP)

| #define USB_GRXSTSR_HOSTMODE_PktSts_IN_TRSF_CPL 0x3 |

Represents paket status information as in receive status pop register(GRXSTSP)

| #define USBH0_MAX_PIPE_NUM (14U) |

Representation of number of pipes available

| #define USBH_PIPE_GET_INDEX | ( | handle | ) | (((uint32_t)handle - (uint32_t)USB0_CH0_BASE)/(0x20U)) |

Macro provides index of the USB channel based on its base address

| #define XMC_USB_DRIVE_PORT1 P3_2 |

Default port(PORT3, pin 2) used to enable VBUS voltage regulator on the board

| #define XMC_USB_DRIVE_PORT2 P0_1 |

Alternate port that can be used to enable VBUS voltage regulator(PORT0, pin 1)

| #define XMC_USBH_API_VERSION ((uint16_t)((uint16_t)XMC_LIB_MAJOR_VERSION << 8U) |XMC_LIB_MINOR_VERSION) |

USBH low level driver API version

| #define XMC_USBH_CLOCK_GATING_DISABLE 0 |

Used to disable clock gating when the driver is fully powered

| #define XMC_USBH_CLOCK_GATING_ENABLE 1 |

Used to enable clock gating when the driver is powered down

| #define XMC_USBH_DRIVER_ERROR -1 |

Unspecified error

| #define XMC_USBH_DRIVER_ERROR_BUSY -2 |

Driver is busy

| #define XMC_USBH_DRIVER_ERROR_PARAMETER -5 |

Parameter error

| #define XMC_USBH_DRIVER_ERROR_SPECIFIC -6 |

Start of driver specific errors

| #define XMC_USBH_DRIVER_ERROR_TIMEOUT -3 |

Timeout occurred

| #define XMC_USBH_DRIVER_ERROR_UNSUPPORTED -4 |

Operation not supported

| #define XMC_USBH_DRIVER_OK 0 |

Operation succeeded

| #define XMC_USBH_ENDPOINT_BULK 2 |

Bulk Endpoint

| #define XMC_USBH_ENDPOINT_CONTROL 0 |

Control Endpoint

| #define XMC_USBH_ENDPOINT_INTERRUPT 3 |

Interrupt Endpoint

| #define XMC_USBH_ENDPOINT_ISOCHRONOUS 1 |

Isochronous Endpoint

| #define XMC_USBH_EP_HANDLE XMC_USBH_PIPE_HANDLE |

Legacy name for pipe handle used by CMSIS

| #define XMC_USBH_EVENT_BUS_ERROR (1UL << 6) |

Bus Error detected

| #define XMC_USBH_EVENT_CONNECT (1UL << 0) |

USB Device Connected to Port

| #define XMC_USBH_EVENT_DISCONNECT (1UL << 1) |

USB Device Disconnected from Port

| #define XMC_USBH_EVENT_HANDSHAKE_ERR (1UL << 5) |

ERR Handshake received

| #define XMC_USBH_EVENT_HANDSHAKE_MDATA (1UL << 3) |

MDATA Handshake received

| #define XMC_USBH_EVENT_HANDSHAKE_NAK (1UL << 1) |

NAK Handshake received

| #define XMC_USBH_EVENT_HANDSHAKE_NYET (1UL << 2) |

NYET Handshake received

| #define XMC_USBH_EVENT_HANDSHAKE_STALL (1UL << 4) |

STALL Handshake received

| #define XMC_USBH_EVENT_OVERCURRENT (1UL << 2) |

USB Device caused Overcurrent

| #define XMC_USBH_EVENT_REMOTE_WAKEUP (1UL << 6) |

USB Device activated Remote Wakeup

| #define XMC_USBH_EVENT_RESET (1UL << 3) |

USB Reset completed

| #define XMC_USBH_EVENT_RESUME (1UL << 5) |

USB Resume occurred

| #define XMC_USBH_EVENT_SUSPEND (1UL << 4) |

USB Suspend occurred

| #define XMC_USBH_EVENT_TRANSFER_COMPLETE (1UL << 0) |

Transfer completed

| #define XMC_USBH_PACKET_CSPLIT (0x0CUL << XMC_USBH_PACKET_SPLIT_Pos) |

CSPLIT Packet

| #define XMC_USBH_PACKET_DATA0 (0x01UL << XMC_USBH_PACKET_DATA_Pos) |

DATA0 PID

| #define XMC_USBH_PACKET_DATA1 (0x02UL << XMC_USBH_PACKET_DATA_Pos) |

DATA1 PID

| #define XMC_USBH_PACKET_DATA_Msk (0x0FUL << XMC_USBH_PACKET_DATA_Pos) |

Packet data PID mask

| #define XMC_USBH_PACKET_DATA_Pos 4 |

Packet data PID position

| #define XMC_USBH_PACKET_IN (0x03UL << XMC_USBH_PACKET_TOKEN_Pos) |

IN Packet

| #define XMC_USBH_PACKET_OUT (0x02UL << XMC_USBH_PACKET_TOKEN_Pos) |

OUT Packet

| #define XMC_USBH_PACKET_PING (0x04UL << XMC_USBH_PACKET_TOKEN_Pos) |

PING Packet

| #define XMC_USBH_PACKET_PRE (1UL << 12) |

PRE Token

| #define XMC_USBH_PACKET_SETUP (0x01UL << XMC_USBH_PACKET_TOKEN_Pos) |

SETUP Packet

| #define XMC_USBH_PACKET_SSPLIT (0x08UL << XMC_USBH_PACKET_SPLIT_Pos) |

SSPLIT Packet

| #define XMC_USBH_PACKET_SSPLIT_E (0x0AUL << XMC_USBH_PACKET_SPLIT_Pos) |

SSPLIT Packet: Data End

| #define XMC_USBH_PACKET_SSPLIT_S (0x09UL << XMC_USBH_PACKET_SPLIT_Pos) |

SSPLIT Packet: Data Start

| #define XMC_USBH_PACKET_SSPLIT_S_E (0x0BUL << XMC_USBH_PACKET_SPLIT_Pos) |

SSPLIT Packet: Data All

| #define XMC_USBH_PACKET_TOKEN_Msk (0x0FUL << XMC_USBH_PACKET_TOKEN_Pos) |

Packet token mask

| #define XMC_USBH_PACKET_TOKEN_Pos 0 |

Packet token position

| #define XMC_USBH_SignalEndpointEvent_t XMC_USBH_SignalPipeEvent_t |

Legacy name for the pipe event handler

| #define XMC_USBH_SPEED_FULL 1U |

Full-speed USB

| #define XMC_USBH_SPEED_HIGH 2U |

High-speed USB

| #define XMC_USBH_SPEED_LOW 0U |

Low-speed USB

| typedef void(* XMC_USBH_SignalPipeEvent_t) (XMC_USBH_PIPE_HANDLE pipe_hndl, uint32_t event) |

Pointer to ARM_USBH_SignalPipeEvent : Signal Pipe Event.

| typedef void(* XMC_USBH_SignalPortEvent_t) (uint8_t port, uint32_t event) |

Pointer to ARM_USBH_SignalPortEvent : Signal Root HUB Port Event.

| uint32_t XMC_USBH_GetInterruptStatus | ( | void | ) |

| void XMC_USBH_HandleIrq | ( | uint32_t | gintsts | ) |

| gintsts | USB global interrupt status. |

| uint8_t XMC_USBH_osDelay | ( | uint32_t | ms | ) |

| ms | Delay in milliseconds. |

| void XMC_USBH_Select_VBUS | ( | XMC_GPIO_PORT_t * | port, |

| uint32_t | pin | ||

| ) |

| port | Address of the port which has the pin used to enable VBUS charge pump. |

| pin | Pin number in the port selected in previous argument using which the VBUS charge pump has to be enabled. |

| void XMC_USBH_TurnOffResumeBit | ( | void | ) |