Data Structures | |

| struct | XMC_SCU_CLOCK_CONFIG_t |

| struct | XMC_SCU_SUPPLYMONITOR_t |

Macros | |

| #define | XMC_BMI_ADDR (0x10000e00U) |

| #define | XMC_SCU_BMI_CANCLK_DCO1 (0U << 11) |

| #define | XMC_SCU_BMI_CANCLK_OSCHP (1U << 11) |

| #define | XMC_SCU_BMI_DAPDIS_CHANNEL_0 (0U << 9) |

| #define | XMC_SCU_BMI_DAPDIS_CHANNEL_1 (1U << 9) |

| #define | XMC_SCU_BMI_DAPTYP_SPD (1U << 8) |

| #define | XMC_SCU_BMI_DAPTYP_SWD (0U << 8) |

| #define | XMC_SCU_BMI_HWCFG_ASC_BSL (0x0040U) |

| #define | XMC_SCU_BMI_HWCFG_ASC_BSLTO (0x0050U) |

| #define | XMC_SCU_BMI_HWCFG_CAN_BSL (0x0000U) |

| #define | XMC_SCU_BMI_HWCFG_CAN_BSLTO (0x0010U) |

| #define | XMC_SCU_BMI_HWCFG_PINDIS (0x0080U) |

| #define | XMC_SCU_BMI_HWCFG_SBSL (0x007AU) |

| #define | XMC_SCU_BMI_HWCFG_SBSL_CANOPEN (0x0020U) |

| #define | XMC_SCU_BMI_HWCFG_SSC_BSL (0x0048U) |

| #define | XMC_SCU_BMI_HWCFG_SSC_BSLTO (0x0058U) |

| #define | XMC_SCU_BMI_HWCFG_UMD (0x0043U) |

| #define | XMC_SCU_BMI_HWCFG_UMHAR (0x0047U) |

| #define | XMC_SCU_BMI_HWCFG_UPM (0x0041U) |

| #define | XMC_SCU_INTERRUPT_EVENT_ACMP0 SCU_INTERRUPT_SRMSK_ACMP0I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ACMP1 SCU_INTERRUPT_SRMSK_ACMP1I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ACMP2 SCU_INTERRUPT_SRMSK_ACMP2I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ACMP3 (((int64_t)SCU_INTERRUPT_SRMSK1_ACMP3I_Msk) << 32U) |

| #define | XMC_SCU_INTERRUPT_EVENT_DCO1_OUT_SYNC (((int64_t)SCU_INTERRUPT_SRMSK1_DCO1OFSI_Msk) << 32U) |

| #define | XMC_SCU_INTERRUPT_EVENT_FLASH_COMPLETED SCU_INTERRUPT_SRCLR_FLCMPLTI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_FLASH_ERROR SCU_INTERRUPT_SRMSK_FLECC2I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_LOCI SCU_INTERRUPT_SRMSK_LOCI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_LOSS_EXT_CLOCK (((int64_t)SCU_INTERRUPT_SRMSK1_LOECI_Msk) << 32U) |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC0 SCU_INTERRUPT_SRMSK_ORC0I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC1 SCU_INTERRUPT_SRMSK_ORC1I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC2 SCU_INTERRUPT_SRMSK_ORC2I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC3 SCU_INTERRUPT_SRMSK_ORC3I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC4 SCU_INTERRUPT_SRMSK_ORC4I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC5 SCU_INTERRUPT_SRMSK_ORC5I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC6 SCU_INTERRUPT_SRMSK_ORC6I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_ORC7 SCU_INTERRUPT_SRMSK_ORC7I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_PEMCAN (((int64_t)SCU_INTERRUPT_SRMSK1_PEMCI_Msk) << 32U) |

| #define | XMC_SCU_INTERRUPT_EVENT_PESRAM SCU_INTERRUPT_SRMSK_PESRAMI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_PEUSIC0 SCU_INTERRUPT_SRMSK_PEU0I_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_PEUSIC1 (((int64_t)SCU_INTERRUPT_SRMSK1_PEU1I_Msk) << 32U) |

| #define | XMC_SCU_INTERRUPT_EVENT_RTC_ALARM SCU_INTERRUPT_SRCLR_AI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_RTC_PERIODIC SCU_INTERRUPT_SRCLR_PI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_RTCATIM0_UPDATED SCU_INTERRUPT_SRMSK_RTC_ATIM0_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_RTCATIM1_UPDATED SCU_INTERRUPT_SRMSK_RTC_ATIM1_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_RTCCTR_UPDATED SCU_INTERRUPT_SRMSK_RTC_CTR_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_RTCTIM0_UPDATED SCU_INTERRUPT_SRMSK_RTC_TIM0_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_RTCTIM1_UPDATED SCU_INTERRUPT_SRMSK_RTC_TIM1_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_STDBYCLKFAIL SCU_INTERRUPT_SRMSK_SBYCLKFI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_TSE_DONE SCU_INTERRUPT_SRMSK_TSE_DONE_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_TSE_HIGH SCU_INTERRUPT_SRMSK_TSE_HIGH_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_TSE_LOW SCU_INTERRUPT_SRMSK_TSE_LOW_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_VCLIP SCU_INTERRUPT_SRMSK_VCLIPI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_VDDPI SCU_INTERRUPT_SRMSK_VDDPI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_VDROP SCU_INTERRUPT_SRMSK_VDROPI_Msk |

| #define | XMC_SCU_INTERRUPT_EVENT_WDT_WARN SCU_INTERRUPT_SRMSK_PRWARN_Msk |

Typedefs | |

| typedef void(* | XMC_SCU_INTERRUPT_EVENT_HANDLER_t) (void) |

| typedef uint32_t | XMC_SCU_INTERRUPT_EVENT_t |

Enumerations | |

| enum | XMC_SCU_CCU_TRIGGER_t |

| enum | XMC_SCU_CLOCK_ADCCLKSRC_t |

| enum | XMC_SCU_CLOCK_DCLKSRC_t |

| enum | XMC_SCU_CLOCK_OSCHP_MODE_t |

| enum | XMC_SCU_CLOCK_OSCLP_MODE_t |

| enum | XMC_SCU_CLOCK_PCLKSRC_t |

| enum | XMC_SCU_CLOCK_RTCCLKSRC_t |

| enum | XMC_SCU_CLOCK_SYNC_CLKSRC_t |

| enum | XMC_SCU_IRQCTRL_t |

| enum | XMC_SCU_PERIPHERAL_CLOCK_t |

| enum | XMC_SCU_POWER_MONITOR_DELAY_t |

| enum | XMC_SCU_POWER_MONITOR_RANGE_t |

| enum | XMC_SCU_RESET_REASON_t |

| enum | XMC_SCU_STATUS_t |

| enum | XMC_SCU_SYSTEM_RESET_REQUEST_t |

System control unit is the SoC power, reset and a clock manager with additional responsibility of providing system stability protection and other auxiliary functions.

SCU provides the following features,

The SCU driver is divided in to clock control logic, reset control logic, system interrupt control logic and miscellaneous control logic.

Clock driver features:

Reset driver features:

Interrupt driver features:

Miscellaneous features:

| #define XMC_BMI_ADDR (0x10000e00U) |

Boot Mode Index (BMI) address holding information about start-up mode and debug configuration of the device.

| #define XMC_SCU_BMI_CANCLK_DCO1 (0U << 11) |

Synchronous CAN clock via internal oscillator (DCO1) with enabled trimming via external reference is selected

| #define XMC_SCU_BMI_CANCLK_OSCHP (1U << 11) |

Synchronous CAN clock via external oscillator (OSC_HP) is selected

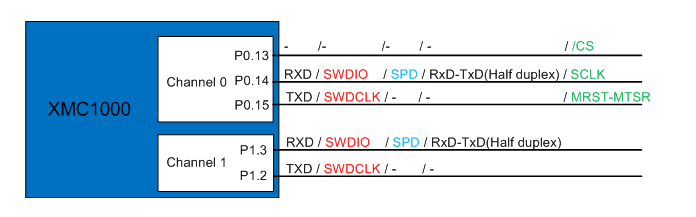

| #define XMC_SCU_BMI_DAPDIS_CHANNEL_0 (0U << 9) |

SWD/SPD_0 pin is selected

| #define XMC_SCU_BMI_DAPDIS_CHANNEL_1 (1U << 9) |

SWD/SPD_1 pin is selected

| #define XMC_SCU_BMI_DAPTYP_SPD (1U << 8) |

Single pin debug (SPD) interface is selected

| #define XMC_SCU_BMI_DAPTYP_SWD (0U << 8) |

Serial wire debug (SWD) interface is selected

| #define XMC_SCU_BMI_HWCFG_ASC_BSL (0x0040U) |

ASC Bootstrap Loader Start-up Mode

| #define XMC_SCU_BMI_HWCFG_ASC_BSLTO (0x0050U) |

ASC BSL Start-up Mode with time-out

| #define XMC_SCU_BMI_HWCFG_CAN_BSL (0x0000U) |

CAN Bootstrap Loader Start-up Mode

| #define XMC_SCU_BMI_HWCFG_CAN_BSLTO (0x0010U) |

CAN Bootstrap Loader Start-up Mode with time-out

| #define XMC_SCU_BMI_HWCFG_PINDIS (0x0080U) |

Boot Configuration Type Selection, Boot from BMI is selected

| #define XMC_SCU_BMI_HWCFG_SBSL (0x007AU) |

Secure Bootstrap Loader Start-up Mode over ASC

| #define XMC_SCU_BMI_HWCFG_SBSL_CANOPEN (0x0020U) |

Secure Bootstrap Loader Start-up Mode over CANopen

| #define XMC_SCU_BMI_HWCFG_SSC_BSL (0x0048U) |

SSC Bootstrap Loader Start-up Mode

| #define XMC_SCU_BMI_HWCFG_SSC_BSLTO (0x0058U) |

SSC BSL Start-up Mode with time-out

| #define XMC_SCU_BMI_HWCFG_UMD (0x0043U) |

User Start-up Mode with debug enabled

| #define XMC_SCU_BMI_HWCFG_UMHAR (0x0047U) |

User Start-up Mode with debug enabled and halt after reset (HAR)

| #define XMC_SCU_BMI_HWCFG_UPM (0x0041U) |

User productive Start-up Mode

| #define XMC_SCU_INTERRUPT_EVENT_ACMP0 SCU_INTERRUPT_SRMSK_ACMP0I_Msk |

Analog comparator-0 output event.

| #define XMC_SCU_INTERRUPT_EVENT_ACMP1 SCU_INTERRUPT_SRMSK_ACMP1I_Msk |

Analog comparator-1 output event.

| #define XMC_SCU_INTERRUPT_EVENT_ACMP2 SCU_INTERRUPT_SRMSK_ACMP2I_Msk |

Analog comparator-2 output event.

| #define XMC_SCU_INTERRUPT_EVENT_ACMP3 (((int64_t)SCU_INTERRUPT_SRMSK1_ACMP3I_Msk) << 32U) |

Analog comparator-3 output event.

| #define XMC_SCU_INTERRUPT_EVENT_DCO1_OUT_SYNC (((int64_t)SCU_INTERRUPT_SRMSK1_DCO1OFSI_Msk) << 32U) |

DCO1 Out of SYNC Event.

| #define XMC_SCU_INTERRUPT_EVENT_FLASH_COMPLETED SCU_INTERRUPT_SRCLR_FLCMPLTI_Msk |

Flash operation completion event.

| #define XMC_SCU_INTERRUPT_EVENT_FLASH_ERROR SCU_INTERRUPT_SRMSK_FLECC2I_Msk |

Flash ECC double bit error event.

| #define XMC_SCU_INTERRUPT_EVENT_LOCI SCU_INTERRUPT_SRMSK_LOCI_Msk |

Loss of clock event.

| #define XMC_SCU_INTERRUPT_EVENT_LOSS_EXT_CLOCK (((int64_t)SCU_INTERRUPT_SRMSK1_LOECI_Msk) << 32U) |

Loss of external OSC_HP clock event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC0 SCU_INTERRUPT_SRMSK_ORC0I_Msk |

Out of range comparator-0 event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC1 SCU_INTERRUPT_SRMSK_ORC1I_Msk |

Out of range comparator-1 event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC2 SCU_INTERRUPT_SRMSK_ORC2I_Msk |

Out of range comparator-2 event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC3 SCU_INTERRUPT_SRMSK_ORC3I_Msk |

Out of range comparator-3 event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC4 SCU_INTERRUPT_SRMSK_ORC4I_Msk |

Out of range comparator-4 event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC5 SCU_INTERRUPT_SRMSK_ORC5I_Msk |

Out of range comparator-5 event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC6 SCU_INTERRUPT_SRMSK_ORC6I_Msk |

Out of range comparator-6 event.

| #define XMC_SCU_INTERRUPT_EVENT_ORC7 SCU_INTERRUPT_SRMSK_ORC7I_Msk |

Out of range comparator-7 event.

| #define XMC_SCU_INTERRUPT_EVENT_PEMCAN (((int64_t)SCU_INTERRUPT_SRMSK1_PEMCI_Msk) << 32U) |

MultiCAN SRAM Parity Error Event.

| #define XMC_SCU_INTERRUPT_EVENT_PESRAM SCU_INTERRUPT_SRMSK_PESRAMI_Msk |

PSRAM Parity error event.

| #define XMC_SCU_INTERRUPT_EVENT_PEUSIC0 SCU_INTERRUPT_SRMSK_PEU0I_Msk |

USIC0 Parity error event.

| #define XMC_SCU_INTERRUPT_EVENT_PEUSIC1 (((int64_t)SCU_INTERRUPT_SRMSK1_PEU1I_Msk) << 32U) |

USIC1 Parity error event.

| #define XMC_SCU_INTERRUPT_EVENT_RTC_ALARM SCU_INTERRUPT_SRCLR_AI_Msk |

RTC alarm event.

| #define XMC_SCU_INTERRUPT_EVENT_RTC_PERIODIC SCU_INTERRUPT_SRCLR_PI_Msk |

RTC periodic event.

| #define XMC_SCU_INTERRUPT_EVENT_RTCATIM0_UPDATED SCU_INTERRUPT_SRMSK_RTC_ATIM0_Msk |

RTCATIM0 register update event.

| #define XMC_SCU_INTERRUPT_EVENT_RTCATIM1_UPDATED SCU_INTERRUPT_SRMSK_RTC_ATIM1_Msk |

RTCATIM1 register update event.

| #define XMC_SCU_INTERRUPT_EVENT_RTCCTR_UPDATED SCU_INTERRUPT_SRMSK_RTC_CTR_Msk |

RTCCTR register update event.

| #define XMC_SCU_INTERRUPT_EVENT_RTCTIM0_UPDATED SCU_INTERRUPT_SRMSK_RTC_TIM0_Msk |

RTCTIM0 register update event.

| #define XMC_SCU_INTERRUPT_EVENT_RTCTIM1_UPDATED SCU_INTERRUPT_SRMSK_RTC_TIM1_Msk |

RTCTIM1 register update event.

| #define XMC_SCU_INTERRUPT_EVENT_STDBYCLKFAIL SCU_INTERRUPT_SRMSK_SBYCLKFI_Msk |

Standby clock failure event.

| #define XMC_SCU_INTERRUPT_EVENT_TSE_DONE SCU_INTERRUPT_SRMSK_TSE_DONE_Msk |

Temperature measurement Completion event.

| #define XMC_SCU_INTERRUPT_EVENT_TSE_HIGH SCU_INTERRUPT_SRMSK_TSE_HIGH_Msk |

Temperature too high event.

| #define XMC_SCU_INTERRUPT_EVENT_TSE_LOW SCU_INTERRUPT_SRMSK_TSE_LOW_Msk |

Temperature too low event.

| #define XMC_SCU_INTERRUPT_EVENT_VCLIP SCU_INTERRUPT_SRMSK_VCLIPI_Msk |

VCLIP event.

| #define XMC_SCU_INTERRUPT_EVENT_VDDPI SCU_INTERRUPT_SRMSK_VDDPI_Msk |

VDDP pre-warning event.

| #define XMC_SCU_INTERRUPT_EVENT_VDROP SCU_INTERRUPT_SRMSK_VDROPI_Msk |

VDROP event.

| #define XMC_SCU_INTERRUPT_EVENT_WDT_WARN SCU_INTERRUPT_SRMSK_PRWARN_Msk |

WDT pre-warning event.

| typedef void(* XMC_SCU_INTERRUPT_EVENT_HANDLER_t) (void) |

Function pointer type used for registering callback functions on SCU event occurrence.

| typedef uint32_t XMC_SCU_INTERRUPT_EVENT_t |

Defines list of events that can generate SCU interrupt. These enums can be used to configure events in SRMSK register for assertion of interrupt. All the enum items are tabulated as per bits present in SRMSK register. Use type XMC_SCU_INTERRUPT_EVENT_t for accessing these enum parameters. These enums can also be used for checking the status of events from the SRSTAT register.

Defines options for Capture/Compare unit timer slice trigger that enables synchronous start function available on the SCU, CCUCON register. Use type XMC_SCU_CCU_TRIGGER_t for accessing these enum parameters.

OSCHP mode

Defines possible sources of peripheral clock (PCLK). These enums can be used to configure PCLKSEL bits of CLKCR Clock Control Register. Use type XMC_SCU_CLOCK_PCLKSRC_t for accessing these enum parameters.

| Enumerator | |

|---|---|

| XMC_SCU_CLOCK_PCLKSRC_MCLK | MCLK as the source for PCLK. |

| XMC_SCU_CLOCK_PCLKSRC_DOUBLE_MCLK | Source of PCLK is twice the MCLK. |

Defines possible sources of RTC clock. These enums can be used to configure RTCCLKSEL bits of CLKCR Clock Control Register. Use type XMC_SCU_CLOCK_RTCCLKSRC_t for accessing these enum parameters.

Clock source for synchronization

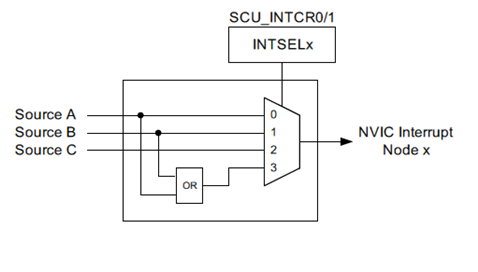

| enum XMC_SCU_IRQCTRL_t |

Selects the service request connected to the interrupt node.

| Enumerator | |

|---|---|

| XMC_SCU_IRQCTRL_SCU_SR0_IRQ0 | SCU_SR0 connected to IRQ0 |

| XMC_SCU_IRQCTRL_CAN0_SR0_IRQ0 | CAN0_SR0 connected to IRQ0 |

| XMC_SCU_IRQCTRL_CCU40_SR0_IRQ0 | CCU40_SR0 connected to IRQ0 |

| XMC_SCU_IRQCTRL_SCU_SR0_OR_CAN0_SR0_IRQ0 | SCU_SR0 and CAN_SR0 are both connected to IRQ0 |

| XMC_SCU_IRQCTRL_SCU_SR1_IRQ1 | SCU_SR1 connected to IRQ1 |

| XMC_SCU_IRQCTRL_CAN0_SR1_IRQ1 | CAN0_SR1 connected to IRQ1 |

| XMC_SCU_IRQCTRL_CCU80_SR0_IRQ1 | CCU80_SR0 connected to IRQ1 |

| XMC_SCU_IRQCTRL_SCU_SR1_OR_CAN0_SR1_IRQ1 | SCU_SR1 and CAN0_SR1 connected to IRQ1 |

| XMC_SCU_IRQCTRL_SCU_SR2_IRQ2 | SCU_SR2 connected to IRQ2 |

| XMC_SCU_IRQCTRL_CAN0_SR2_IRQ2 | CAN0_SR2 connected to IRQ2 |

| XMC_SCU_IRQCTRL_CCU80_SR1_IRQ2 | CCU80_SR1 connected to IRQ2 |

| XMC_SCU_IRQCTRL_SCU_SR2_OR_CAN0_SR2_IRQ2 | SCU_SR2 and CAN0_SR2 connected to IRQ2 |

| XMC_SCU_IRQCTRL_ERU0_SR0_IRQ3 | ERU0_SR0 connected to IRQ3 |

| XMC_SCU_IRQCTRL_ERU1_SR0_IRQ3 | ERU1_SR0 connected to IRQ3 |

| XMC_SCU_IRQCTRL_CAN0_SR0_IRQ3 | CAN0_SR0 connected to IRQ3 |

| XMC_SCU_IRQCTRL_ERU0_SR0_OR_ERU1_SR0_IRQ3 | ERU0_SR0 and ERU1_SR0 connected to IRQ3 |

| XMC_SCU_IRQCTRL_ERU0_SR1_IRQ4 | ERU0_SR1 connected to IRQ4 |

| XMC_SCU_IRQCTRL_ERU1_SR1_IRQ4 | ERU1_SR1 connected to IRQ4 |

| XMC_SCU_IRQCTRL_CAN0_SR1_IRQ4 | CAN0_SR1 connected to IRQ4 |

| XMC_SCU_IRQCTRL_ERU0_SR1_OR_ERU1_SR1_IRQ4 | ERU0_SR1 and ERU1_SR1 connected to IRQ4 |

| XMC_SCU_IRQCTRL_ERU0_SR2_IRQ5 | ERU0_SR2 connected to IRQ5 |

| XMC_SCU_IRQCTRL_ERU1_SR2_IRQ5 | ERU1_SR2 connected to IRQ5 |

| XMC_SCU_IRQCTRL_CAN0_SR2_IRQ5 | CAN0_SR2 connected to IRQ5 |

| XMC_SCU_IRQCTRL_ERU0_SR2_OR_ERU1_SR2_IRQ5 | ERU0_SR2 and ERU1_SR2 connected to IRQ5 |

| XMC_SCU_IRQCTRL_ERU0_SR3_IRQ6 | ERU0_SR3 connected to IRQ6 |

| XMC_SCU_IRQCTRL_ERU1_SR3_IRQ6 | ERU1_SR3 connected to IRQ6 |

| XMC_SCU_IRQCTRL_CAN0_SR3_IRQ6 | CAN0_SR3 connected to IRQ6 |

| XMC_SCU_IRQCTRL_ERU0_SR3_OR_ERU1_SR3_IRQ6 | ERU0_SR3 and ERU1_SR3 connected to IRQ6 |

| XMC_SCU_IRQCTRL_MATH_SR0_IRQ7 | MATH_SR0 connected to IRQ7 |

| XMC_SCU_IRQCTRL_CAN0_SR3_IRQ7 | CAN0_SR3 connected to IRQ7 |

| XMC_SCU_IRQCTRL_CCU40_SR1_IRQ7 | CCU40_SR1 connected to IRQ7 |

| XMC_SCU_IRQCTRL_MATH_SR0_OR_CAN0_SR3_IRQ7 | MATH_SR0 and CAN0_SR3 connected to IRQ7 |

| XMC_SCU_IRQCTRL_LEDTS2_SR0_IRQ8 | LEDTS2_SR0 connected to IRQ8 |

| XMC_SCU_IRQCTRL_CCU40_SR0_IRQ8 | CCU40_SR0 connected to IRQ8 |

| XMC_SCU_IRQCTRL_CCU80_SR0_IRQ8 | CCU80_SR0 connected to IRQ8 |

| XMC_SCU_IRQCTRL_LEDTS2_SR0_OR_CCU40_SR0_IRQ8 | LEDTS2_SR0 and CCU40_SR0 connected to IRQ8 |

| XMC_SCU_IRQCTRL_USIC0_SR0_IRQ9 | USIC0_SR0 connected to IRQ9 |

| XMC_SCU_IRQCTRL_USIC1_SR0_IRQ9 | USIC1_SR0 connected to IRQ9 |

| XMC_SCU_IRQCTRL_ERU0_SR0_IRQ9 | ERU0_SR0 connected to IRQ9 |

| XMC_SCU_IRQCTRL_USIC0_SR0_OR_USIC1_SR0_IRQ9 | USIC0_SR0 and USIC1_SR0 connected to IRQ9 |

| XMC_SCU_IRQCTRL_USIC0_SR1_IRQ10 | USIC0_SR1 connected to IRQ10 |

| XMC_SCU_IRQCTRL_USIC1_SR1_IRQ10 | USIC1_SR1 connected to IRQ10 |

| XMC_SCU_IRQCTRL_ERU0_SR1_IRQ10 | ERU0_SR1 connected to IRQ10 |

| XMC_SCU_IRQCTRL_USIC0_SR1_OR_USIC1_SR1_IRQ10 | USIC0_SR1 and USIC1_SR1 connected to IRQ10 |

| XMC_SCU_IRQCTRL_USIC0_SR2_IRQ11 | USIC0_SR2 connected to IRQ11 |

| XMC_SCU_IRQCTRL_USIC1_SR2_IRQ11 | USIC1_SR2 connected to IRQ11 |

| XMC_SCU_IRQCTRL_ERU0_SR2_IRQ11 | ERU0_SR2 connected to IRQ11 |

| XMC_SCU_IRQCTRL_USIC0_SR2_OR_USIC1_SR2_IRQ11 | USIC0_SR2 and USIC1_SR2 connected to IRQ11 |

| XMC_SCU_IRQCTRL_USIC0_SR3_IRQ12 | USIC0_SR3 connected to IRQ12 |

| XMC_SCU_IRQCTRL_USIC1_SR3_IRQ12 | USIC1_SR3 connected to IRQ12 |

| XMC_SCU_IRQCTRL_ERU0_SR3_IRQ12 | ERU0_SR3 connected to IRQ12 |

| XMC_SCU_IRQCTRL_USIC0_SR3_OR_USIC1_SR3_IRQ12 | USIC0_SR3 and USIC1_SR3 connected to IRQ12 |

| XMC_SCU_IRQCTRL_USIC0_SR4_IRQ13 | USIC0_SR4 connected to IRQ13 |

| XMC_SCU_IRQCTRL_USIC1_SR4_IRQ13 | USIC1_SR4 connected to IRQ13 |

| XMC_SCU_IRQCTRL_CCU80_SR1_IRQ13 | CCU80_SR1 connected to IRQ13 |

| XMC_SCU_IRQCTRL_USIC0_SR4_OR_USIC1_SR4_IRQ13 | USIC0_SR4 and USIC1_SR4 connected to IRQ13 |

| XMC_SCU_IRQCTRL_USIC0_SR5_IRQ14 | USIC0_SR5 connected to IRQ14 |

| XMC_SCU_IRQCTRL_USIC1_SR5_IRQ14 | USIC1_SR5 connected to IRQ14 |

| XMC_SCU_IRQCTRL_POSIF0_SR0_IRQ14 | POSIF0_SR0 connected to IRQ14 |

| XMC_SCU_IRQCTRL_USIC0_SR5_OR_USIC1_SR5_IRQ14 | USIC0_SR5 and USIC1_SR5 connected to IRQ14 |

| XMC_SCU_IRQCTRL_VADC0_C0SR0_IRQ15 | VADC0_C0SR0 connected to IRQ15 |

| XMC_SCU_IRQCTRL_USIC0_SR0_IRQ15 | USIC0_SR0 connected to IRQ15 |

| XMC_SCU_IRQCTRL_POSIF0_SR1_IRQ15 | POSIF0_SR1 connected to IRQ15 |

| XMC_SCU_IRQCTRL_VADC0_C0SR0_OR_USIC0_SR0_IRQ15 | VADC0_C0SR0 and USIC0_SR0 connected to IRQ15 |

| XMC_SCU_IRQCTRL_VADC0_C0SR1_IRQ16 | VADC0_C0SR1 connected to IRQ16 |

| XMC_SCU_IRQCTRL_USIC0_SR1_IRQ16 | USIC0_SR1 connected to IRQ16 |

| XMC_SCU_IRQCTRL_CCU40_SR2_IRQ16 | CCU40_SR2 connected to IRQ16 |

| XMC_SCU_IRQCTRL_VADC0_C0SR1_OR_USIC0_SR1_IRQ16 | VADC0_C0SR1 and USIC0_SR1 connected to IRQ16 |

| XMC_SCU_IRQCTRL_VADC0_G0SR0_IRQ17 | VADC0_G0SR0 connected to IRQ17 |

| XMC_SCU_IRQCTRL_USIC0_SR2_IRQ17 | USIC0_SR2 connected to IRQ17 |

| XMC_SCU_IRQCTRL_CAN0_SR0_IRQ17 | CAN0_SR0 connected to IRQ17 |

| XMC_SCU_IRQCTRL_VADC0_G0SR0_OR_USIC0_SR2_IRQ17 | VADC0_G0SR0 and USIC0_SR2 connected to IRQ17 |

| XMC_SCU_IRQCTRL_VADC0_G0SR1_IRQ18 | VADC0_G0SR1 connected to IRQ18 |

| XMC_SCU_IRQCTRL_USIC0_SR3_IRQ18 | USIC0_SR3 connected to IRQ18 |

| XMC_SCU_IRQCTRL_CAN0_SR1_IRQ18 | CAN0_SR1 connected to IRQ18 |

| XMC_SCU_IRQCTRL_VADC0_G0SR1_OR_USIC0_SR3_IRQ18 | VADC0_G0SR1 and USIC0_SR3 connected to IRQ18 |

| XMC_SCU_IRQCTRL_VADC0_G1SR0_IRQ19 | VADC0_G1SR0 connected to IRQ19 |

| XMC_SCU_IRQCTRL_USIC0_SR4_IRQ19 | USIC0_SR4 connected to IRQ19 |

| XMC_SCU_IRQCTRL_CAN0_SR2_IRQ19 | CAN0_SR2 connected to IRQ19 |

| XMC_SCU_IRQCTRL_VADC0_G1SR0_OR_USIC0_SR4_IRQ19 | VADC0_G1SR0 and USIC0_SR4 connected to IRQ19 |

| XMC_SCU_IRQCTRL_VADC0_G1SR1_IRQ20 | VADC0_G1SR1 connected to IRQ20 |

| XMC_SCU_IRQCTRL_USIC0_SR5_IRQ20 | USIC0_SR5 connected to IRQ20 |

| XMC_SCU_IRQCTRL_CAN0_SR3_IRQ20 | CAN0_SR3 connected to IRQ20 |

| XMC_SCU_IRQCTRL_CAN0_SR4_IRQ20 |

|

| XMC_SCU_IRQCTRL_VADC0_G1SR1_OR_USIC0_SR5_IRQ20 | VADC0_G1SR1 and USIC0_SR5 connected to IRQ20 |

| XMC_SCU_IRQCTRL_CCU40_SR0_IRQ21 | CCU40_SR0 connected to IRQ21 |

| XMC_SCU_IRQCTRL_CCU41_SR0_IRQ21 | CCU41_SR0 connected to IRQ21 |

| XMC_SCU_IRQCTRL_USIC0_SR0_IRQ21 | USIC0_SR0 connected to IRQ21 |

| XMC_SCU_IRQCTRL_CCU40_SR0_OR_CCU41_SR0_IRQ21 | CCU40_SR0 and CCU41_SR0 connected to IRQ21 |

| XMC_SCU_IRQCTRL_CCU40_SR1_IRQ22 | CCU40_SR1 connected to IRQ22 |

| XMC_SCU_IRQCTRL_CCU41_SR1_IRQ22 | CCU41_SR1 connected to IRQ22 |

| XMC_SCU_IRQCTRL_USIC0_SR1_IRQ22 | USIC0_SR1 connected to IRQ22 |

| XMC_SCU_IRQCTRL_CCU40_SR0_OR_CCU41_SR0_IRQ22 | CCU40_SR0 and CCU41_SR0 connected to IRQ22 |

| XMC_SCU_IRQCTRL_CCU40_SR2_IRQ23 | CCU40_SR2 connected to IRQ23 |

| XMC_SCU_IRQCTRL_CCU41_SR2_IRQ23 | CCU41_SR2 connected to IRQ23 |

| XMC_SCU_IRQCTRL_USIC0_SR2_IRQ23 | USIC0_SR2 connected to IRQ23 |

| XMC_SCU_IRQCTRL_CCU40_SR2_OR_CCU41_SR2_IRQ23 | CCU40_SR2 and CCU41_SR2 connected to IRQ23 |

| XMC_SCU_IRQCTRL_CCU40_SR3_IRQ24 | CCU40_SR3 connected to IRQ24 |

| XMC_SCU_IRQCTRL_CCU41_SR3_IRQ24 | CCU41_SR3 connected to IRQ24 |

| XMC_SCU_IRQCTRL_USIC0_SR3_IRQ24 | USIC0_SR3 connected to IRQ24 |

| XMC_SCU_IRQCTRL_CCU40_SR3_OR_CCU41_SR3_IRQ24 | CCU40_SR3 and CCU41_SR3 connected to IRQ24 |

| XMC_SCU_IRQCTRL_CCU80_SR0_IRQ25 | CCU80_SR0 connected to IRQ25 |

| XMC_SCU_IRQCTRL_CCU81_SR0_IRQ25 | CCU81_SR0 connected to IRQ25 |

| XMC_SCU_IRQCTRL_USIC0_SR4_IRQ25 | USIC0_SR4 connected to IRQ25 |

| XMC_SCU_IRQCTRL_CCU80_SR0_OR_CCU81_SR0_IRQ25 | CCU80_SR0 and CCU81_SR0 connected to IRQ25 |

| XMC_SCU_IRQCTRL_CCU80_SR1_IRQ26 | CCU80_SR1 connected to IRQ26 |

| XMC_SCU_IRQCTRL_CCU81_SR1_IRQ26 | CCU81_SR1 connected to IRQ26 |

| XMC_SCU_IRQCTRL_USIC0_SR5_IRQ26 | USIC0_SR5 connected to IRQ26 |

| XMC_SCU_IRQCTRL_CCU80_SR1_OR_CCU81_SR1_IRQ26 | CCU80_SR1 and CCU81_SR1 connected to IRQ26 |

| XMC_SCU_IRQCTRL_POSIF0_SR0_IRQ27 | POSIF0_SR0 connected to IRQ27 |

| XMC_SCU_IRQCTRL_POSIF1_SR0_IRQ27 | POSIF1_SR0 connected to IRQ27 |

| XMC_SCU_IRQCTRL_CCU40_SR3_IRQ27 | CCU40_SR3 connected to IRQ27 |

| XMC_SCU_IRQCTRL_POSIF0_SR0_OR_POSIF1_SR0_IRQ27 | POSIF0_SR0 and POSIF1_SR0 connected to IRQ27 |

| XMC_SCU_IRQCTRL_POSIF0_SR1_IRQ28 | POSIF0_SR1 connected to IRQ28 |

| XMC_SCU_IRQCTRL_POSIF1_SR1_IRQ28 | POSIF1_SR1 connected to IRQ28 |

| XMC_SCU_IRQCTRL_ERU0_SR0_IRQ28 | ERU0_SR0 connected to IRQ28 |

| XMC_SCU_IRQCTRL_POSIF0_SR1_OR_POSIF1_SR1_IRQ28 | POSIF0_SR1 and POSIF1_SR1 connected to IRQ28 |

| XMC_SCU_IRQCTRL_LEDTS0_SR0_IRQ29 | LEDTS0_SR0 connected to IRQ29 |

| XMC_SCU_IRQCTRL_CCU40_SR1_IRQ29 | CCU40_SR1 connected to IRQ29 |

| XMC_SCU_IRQCTRL_ERU0_SR1_IRQ29 | ERU0_SR1 connected to IRQ29 |

| XMC_SCU_IRQCTRL_LEDTS0_SR0_OR_CCU40_SR1_IRQ29 | LEDTS0_SR0 and CCU40_SR1 connected to IRQ29 |

| XMC_SCU_IRQCTRL_LEDTS1_SR0_IRQ30 | LEDTS1_SR0 connected to IRQ30 |

| XMC_SCU_IRQCTRL_CCU40_SR2_IRQ30 | CCU40_SR2 connected to IRQ30 |

| XMC_SCU_IRQCTRL_ERU0_SR2_IRQ30 | ERU0_SR2 connected to IRQ30 |

| XMC_SCU_IRQCTRL_LEDTS0_SR0_OR_CCU40_SR1_IRQ30 | LEDTS0_SR0 and CCU40_SR1 connected to IRQ30 |

| XMC_SCU_IRQCTRL_BCCU0_SR0_IRQ31 | BCCU0_SR0 connected to IRQ31 |

| XMC_SCU_IRQCTRL_CCU40_SR3_IRQ31 | CCU40_SR3 connected to IRQ31 |

| XMC_SCU_IRQCTRL_ERU0_SR3_IRQ31 | ERU0_SR3 connected to IRQ31 |

| XMC_SCU_IRQCTRL_BCCU0_SR0_OR_CCU40_SR3_IRQ31 | BCCU0_SR0 and CCU40_SR3 connected to IRQ31 |

Defines the list of peripherals that support clock gating. After a master reset, only core, memories, SCU and PORT peripheral are not clock gated. The rest of the peripherals are by default clock gated. All the enum items are tabulated as per bits present in CGATSTAT0 register. Use type XMC_SCU_PERIPHERAL_CLOCK_t for accessing these enum parameters.

TODO

TODO

Defines the cause of last reset. The cause of last reset gets automatically stored in the SCU_RSTSTAT register and can be checked by user software to determine the state of the system and for debug purpose. All the enum items are tabulated as per bits present in SCU_RSTSTAT register. Use type XMC_SCU_RESET_REASON_t for accessing these enum parameters.

| enum XMC_SCU_STATUS_t |

Defines the status of SCU API execution, used to verify the SCU related API calls.

Defines the reset sources that can cause device reset. These enums can be used to configure reset source in reset control RSTCON register which enables different reset sources to identify the reset cause. The SCU_RSTSTAT register can be checked by user software to determine the state of the system and for debug purpose. Use type XMC_SCU_SYSTEM_RESET_REQUEST_t for accessing these enum parameters.

| uint32_t XMC_SCU_CalcTemperature | ( | void | ) |

| void XMC_SCU_CLOCK_CalibrateOscillatorOnTemperature | ( | int32_t | temperature | ) |

| temperature | measured temperature using the on-chip temperature sensor |

| void XMC_SCU_CLOCK_ClearDCO1OscillatorWatchdogStatus | ( | void | ) |

| void XMC_SCU_CLOCK_DisableDCO1ExtRefCalibration | ( | void | ) |

| void XMC_SCU_CLOCK_DisableDCO1OscillatorWatchdog | ( | void | ) |

| void XMC_SCU_CLOCK_EnableDCO1ExtRefCalibration | ( | XMC_SCU_CLOCK_SYNC_CLKSRC_t | sync_clk, |

| uint32_t | prescaler, | ||

| uint32_t | syn_preload | ||

| ) |

| sync_clk | Clock source selected as external reference. XMC_SCU_CLOCK_SYNC_CLKSRC_t |

| prescaler | integer( \(\frac{syn_preload \times f_{OSC}[MHz]}{48}\)) |

| syn_preload | max. value 0x1FFF integer( \(\frac{48 \times prescaler}{f_{OSC}[MHz]}\)) |

| void XMC_SCU_CLOCK_EnableDCO1OscillatorWatchdog | ( | void | ) |

| void XMC_SCU_CLOCK_GatePeripheralClock | ( | const XMC_SCU_PERIPHERAL_CLOCK_t | peripheral | ) |

| peripheral | The peripheral for which the clock has to be gated. Range: Use type XMC_SCU_PERIPHERAL_CLOCK_t to identify the peripheral clock to be gated. |

| uint32_t XMC_SCU_CLOCK_GetCpuClockFrequency | ( | void | ) |

| uint32_t XMC_SCU_CLOCK_GetFastPeripheralClockFrequency | ( | void | ) |

| uint32_t XMC_SCU_CLOCK_GetPeripheralClockFrequency | ( | void | ) |

| void XMC_SCU_CLOCK_Init | ( | const XMC_SCU_CLOCK_CONFIG_t *const | config | ) |

| config | Pointer to structure holding the clock prescaler values and divider values for configuring clock generators and clock tree. Range: Configure the members of structure XMC_SCU_CLOCK_CONFIG_t for various parameters of clock setup. |

| bool XMC_SCU_CLOCK_IsDCO1ExtRefCalibrationReady | ( | void | ) |

| bool XMC_SCU_CLOCK_IsPeripheralClockGated | ( | const XMC_SCU_PERIPHERAL_CLOCK_t | peripheral | ) |

| peripheral | The peripheral for which the check for clock gating has to be done. Range: Use type XMC_SCU_PERIPHERAL_CLOCK_t to identify the peripheral. |

| void XMC_SCU_CLOCK_ScaleMCLKFrequency | ( | uint32_t | idiv, |

| uint32_t | fdiv | ||

| ) |

| idiv | Divider value. Range: 0 to 255. |

| fdiv | Fractional Divider value. Range: XMC11/XMC12/XMC13 Device: 0 to 255. XMC14 Device: 0 to 1023. |

| void XMC_SCU_CLOCK_SetAdcClockSrc | ( | XMC_SCU_CLOCK_ADCCLKSRC_t | adcclk_src | ) |

| adcclk_src | Clock source selected as external reference. XMC_SCU_CLOCK_ADCCLKSRC_t |

| void XMC_SCU_CLOCK_SetFastPeripheralClockSource | ( | const XMC_SCU_CLOCK_PCLKSRC_t | source | ) |

| source | Fast peripheral clock source. Range: Use type XMC_SCU_CLOCK_PCLKSRC_t to identify the clock source. XMC_SCU_CLOCK_PCLKSRC_MCLK- Use MCLK as the peripheral clock. XMC_SCU_CLOCK_PCLKSRC_DOUBLE_MCLK- peripheral clock will be 2 times the MCLK frequency. |

| void XMC_SCU_CLOCK_SetHighPerformanceOscillatorMode | ( | XMC_SCU_CLOCK_OSCHP_MODE_t | mode | ) |

| mode | Oscillator mode. XMC_SCU_CLOCK_OSCHP_MODE_t |

| void XMC_SCU_CLOCK_SetLowPerformanceOscillatorMode | ( | XMC_SCU_CLOCK_OSCLP_MODE_t | mode | ) |

| mode | Oscillator mode. XMC_SCU_CLOCK_OSCLP_MODE_t |

| void XMC_SCU_CLOCK_SetMCLKFrequency | ( | uint32_t | freq_khz | ) |

| freq_khz | Required MCLK frequency value in kHz. Range: XMC11/XMC12/XMC13 Device: 125 to 32000. XMC14 Device: 188 to 48000 when DCO1 is clock source for clock control unit. 79 to 48000 when OSC_HP is clock source for clock control unit. |

| void XMC_SCU_CLOCK_UngatePeripheralClock | ( | const XMC_SCU_PERIPHERAL_CLOCK_t | peripheral | ) |

| peripheral | The peripheral for which the clock has to be ungated. Range: Use type XMC_SCU_PERIPHERAL_CLOCK_t to identify the peripheral. |

| void XMC_SCU_DisablePrefetchUnit | ( | void | ) |

This function disables the Prefetch Unit (PFU). The purpose of the Prefetch unit is to reduce the Flash latency gap at higher system frequencies to increase the instruction per cycle performance.

| void XMC_SCU_EnablePrefetchUnit | ( | void | ) |

This function enables the Prefetch Unit (PFU). The purpose of the Prefetch unit is to reduce the Flash latency gap at higher system frequencies to increase the instruction per cycle performance.

| uint32_t XMC_SCU_GetBMI | ( | void | ) |

< Boot Mode Index (BMI) address holding information about start-up mode and debug configuration of the device.

| uint32_t XMC_SCU_GetMirrorStatus | ( | void | ) |

| uint32_t XMC_SCU_GetTemperature | ( | void | ) |

| bool XMC_SCU_HighTemperature | ( | void | ) |

| void XMC_SCU_INTERRUPT_ClearEventStatus | ( | const XMC_SCU_INTERRUPT_EVENT_t | event | ) |

| event | Bit mask of the events to clear. Range: Use type XMC_SCU_INTERRUPT_EVENT_t for providing the input value. Multiple events can be combined using the OR operation. |

| void XMC_SCU_INTERRUPT_DisableEvent | ( | const XMC_SCU_INTERRUPT_EVENT_t | event | ) |

| event | Bit mask of the event to disable. Range: Use type XMC_SCU_INTERRUPT_EVENT_t for providing the input value. Multiple events can be combined using the OR operation. |

| void XMC_SCU_INTERRUPT_EnableEvent | ( | const XMC_SCU_INTERRUPT_EVENT_t | event | ) |

| event | Bit mask of the event to enable. Range: Use type XMC_SCU_INTERRUPT_EVENT_t for providing the input value. Multiple events can be combined using the OR operation. |

| XMC_SCU_STATUS_t XMC_SCU_INTERRUPT_SetEventHandler | ( | const XMC_SCU_INTERRUPT_EVENT_t | event, |

| const XMC_SCU_INTERRUPT_EVENT_HANDLER_t | handler | ||

| ) |

| event | The event for which the interrupt handler is to be configured. Range: Use type XMC_SCU_INTERRUPT_EVENT_t for identifying the event. |

| handler | Name of the function to be executed when the event if detected. Range: The function accepts no arguments and returns no value. |

| void XMC_SCU_INTERRUPT_TriggerEvent | ( | const XMC_SCU_INTERRUPT_EVENT_t | event | ) |

| event | Bit mask of the event to be triggered. Range: Use type XMC_SCU_INTERRUPT_EVENT_t for providing the input value. Multiple events can be combined using the OR operation. |

| XMC_SCU_INTERRUPT_EVENT_t XMC_SCU_INTERUPT_GetEventStatus | ( | void | ) |

| void XMC_SCU_IRQHandler | ( | uint32_t | sr_num | ) |

| sr_num | Service request number identifying the SCU interrupt generated. Range: 0 to 2. XMC4x devices have one common SCU interrupt, so the value should be 0. But XMC1x devices support 3 interrupt nodes. |

| bool XMC_SCU_IsTempMeasurementDone | ( | void | ) |

| void XMC_SCU_LockProtectedBits | ( | void | ) |

| Register | Bit fields |

| SCU_CLKCR | FDIV, IDIV, PCLKSEL, RTCLKSEL |

| SCU_CGATSET0 | All bits |

| SCU_CGATCLR0 | All bits |

| SCU_ANAOFFSET | ADJL_OFFSET |

| VADC0_ACCPROT0 | All bits |

| VADC0_ACCPROT1 | All bits |

| bool XMC_SCU_LowTemperature | ( | void | ) |

| void XMC_SCU_POWER_DisableMonitor | ( | void | ) |

| void XMC_SCU_POWER_EnableMonitor | ( | XMC_SCU_POWER_MONITOR_RANGE_t | range, |

| XMC_SCU_POWER_MONITOR_DELAY_t | delay | ||

| ) |

| range | VDEL Range Select XMC_SCU_POWER_MONITOR_RANGE_t |

| delay | VDEL Timing Setting XMC_SCU_POWER_MONITOR_DELAY_t |

| void XMC_SCU_RESET_AssertMasterReset | ( | void | ) |

| void XMC_SCU_RESET_ClearDeviceResetReason | ( | void | ) |

| void XMC_SCU_RESET_EnableResetRequest | ( | uint32_t | request | ) |

| request | Reset source to trigger the device reset. Range: Use type XMC_SCU_SYSTEM_RESET_REQUEST_t to identify the reset source. XMC_SCU_RESET_REQUEST_FLASH_ECC_ERROR- Reset when flash memory double bit error is detected. XMC_SCU_RESET_REQUEST_CLOCK_LOSS- Reset when loss of clock is detected. XMC_SCU_RESET_REQUEST_SRAM_PARITY_ERROR- Reset when SRAM parity error is detected. XMC_SCU_RESET_REQUEST_USIC_SRAM_PARITY_ERROR- Reset when USIC0 SRAM parity error is detected. |

| uint32_t XMC_SCU_RESET_GetDeviceResetReason | ( | void | ) |

| uint32_t XMC_SCU_SetBMI | ( | uint32_t | flags, |

| uint8_t | timeout | ||

| ) |

| flags | may be any of: XMC_SCU_BMI_HWCFG_CAN_BSL (only available for XMC1400 series with CAN Module) XMC_SCU_BMI_HWCFG_CAN_BSLTO (only available for XMC1400 series with CAN Module) XMC_SCU_BMI_HWCFG_SBSL_CANOPEN (only available for XMC1400 series with CAN Module) XMC_SCU_BMI_HWCFG_ASC_BSL XMC_SCU_BMI_HWCFG_UPM XMC_SCU_BMI_HWCFG_UMD XMC_SCU_BMI_HWCFG_UMHAR XMC_SCU_BMI_HWCFG_SSC_BSL XMC_SCU_BMI_HWCFG_ASC_BSLTO XMC_SCU_BMI_HWCFG_SSC_BSLTO XMC_SCU_BMI_HWCFG_SBSL optionally OR'd together with any of (only available for XMC1400 series): XMC_SCU_BMI_HWCFG_PINDIS optionally OR'd together with any of: XMC_SCU_BMI_DAPTYP_SWD XMC_SCU_BMI_DAPTYP_SPD optionally OR'd together with any of: XMC_SCU_BMI_DAPDIS_CHANNEL_0 XMC_SCU_BMI_DAPDIS_CHANNEL_1

XMC_SCU_BMI_CANCLK_DCO1 XMC_SCU_BMI_CANCLK_OSCHP |

| timeout | Only relevant if a start up mode is selected that uses timeout. The time-out duration is BSLTO*2664000 MCLK cycles, the supported time-out range is 0.3-5s (333...4995ms) |

| void XMC_SCU_SetCcuTriggerHigh | ( | const uint32_t | trigger | ) |

| trigger | CCU slices to be triggered synchronously via software. The value is a bitmask of CCU slice bits in the register CCUCON. Range: Use type XMC_SCU_CCU_TRIGGER_t for bitmask of individual CCU slices. Multiple slices can be combined using OR operation. |

| void XMC_SCU_SetCcuTriggerLow | ( | const uint32_t | trigger | ) |

| trigger | CCU slices to be triggered synchronously via software. The value is a bitmask of CCU slice bits in the register CCUCON. Range: Use type XMC_SCU_CCU_TRIGGER_t for bitmask of individual CCU slices. Multiple slices can be combined using OR operation. |

| void XMC_SCU_SetInterruptControl | ( | uint8_t | irq_number, |

| XMC_SCU_IRQCTRL_t | source | ||

| ) |

This function selects service request source for a NVIC interrupt node. The XMC1400 series has up to 54 peripheral service requests. The Cortex M0 however has 32 interrupts available for peripherals. This function allows you to select which 32 peripheral requests of the 54 the CPU should react on.

| irq_number | Interrupt number, 0 to 31 |

| source | Peripheral service request. See XMC_SCU_IRQCTRL_t |

| void XMC_SCU_SetRawTempLimits | ( | const uint32_t | lower_temp, |

| const uint32_t | upper_temp | ||

| ) |

| lower_temp | Lower threshold value for the die temperature. Range: 0 to 65535(16 bit unsigned value). |

| upper_temp | Upper threshold value for the die temperature. Range: 0 to 65535(16 bit unsigned value). |

| XMC_SCU_STATUS_t XMC_SCU_SetTempHighLimit | ( | uint32_t | limit | ) |

| limit | Kelvin degree temperature higher compare limit in range [233,388] |

| XMC_SCU_STATUS_t XMC_SCU_SetTempLowLimit | ( | uint32_t | limit | ) |

| limit | Kelvin degree temperature lower compare limit in range [233,388] |

| void XMC_SCU_StartTempMeasurement | ( | void | ) |

| void XMC_SCU_StopTempMeasurement | ( | void | ) |

| void XMC_SCU_SupplyMonitorInit | ( | const XMC_SCU_SUPPLYMONITOR_t * | obj | ) |

| obj | Pointer to data structure consisting voltage monitoring block configuration. Range: Use type XMC_SCU_SUPPLYMONITOR_t for detailed description of structure members. |

| void XMC_SCU_UnlockProtectedBits | ( | void | ) |

| Register | Bit fields |

| SCU_CLKCR | FDIV, IDIV, PCLKSEL, RTCLKSEL |

| SCU_CGATSET0 | All bits |

| SCU_CGATCLR0 | All bits |

| SCU_ANAOFFSET | ADJL_OFFSET |

| VADC0_ACCPROT0 | All bits |

| VADC0_ACCPROT1 | All bits |