Configures the DMA Controller block, channels and descriptors.

The functions and other declarations used in this driver are in cy_dmac.h. You can include cy_pdl.h to get access to all functions and declarations in the PDL.

The DMA Controller channel can be used in any project to transfer data without CPU intervention basing on a hardware trigger signal from another component.

The DMA Controller block has a set of registers, a base hardware address, and supports multiple channels. Many API functions for the DMAC driver require a base hardware address and channel number. Ensure that you use the correct hardware address for the DMA Controller block in use.

Features:

To set up a DMAC driver, initialize a descriptor, initialize and enable a channel, and enable the DMAC block.

To set up a descriptor, provide the configuration parameters for the descriptor in the cy_stc_dmac_descriptor_config_t structure. Then call the Cy_DMAC_Descriptor_Init function to initialize the descriptor in SRAM. You can modify the source and destination addresses dynamically by calling Cy_DMAC_Descriptor_SetSrcAddress and Cy_DMAC_Descriptor_SetDstAddress.

To set up a DMAC channel, provide a filled cy_stc_dmac_channel_config_t structure. Call the Cy_DMAC_Channel_Init function, specifying the channel number. Use Cy_DMAC_Channel_Enable to enable the configured DMAC channel.

Call Cy_DMAC_Channel_Enable for each DMAC channel in use.

When configured, another peripheral typically triggers the DMAC channel. The trigger is connected to the DMAC channel using the trigger multiplexer. The trigger multiplexer driver has a software trigger you can use in firmware to trigger the DMAC channel. See the Trigger Multiplexer documentation.

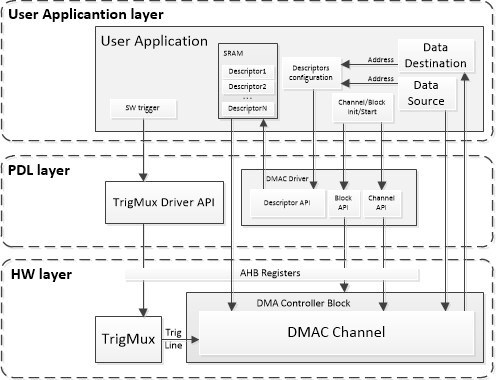

The following is a simplified structure of the DMAC driver API interdependencies in a typical user application:

NOTE: DMAC will read descriptors from SRAM memory. To run DMAC on devices with Core CM7, D cache needs to be cleaned before calling Cy_DMAC_Channel_Enable and should be invalidated after DMAC transfer.

NOTE: Even if a DMAC channel is enabled, it is not operational until the DMAC block is enabled using function Cy_DMAC_Enable.

NOTE: If the DMAC descriptor is configured to generate an interrupt, the interrupt must be enabled using the Cy_DMAC_Channel_SetInterruptMask function for each DMAC channel.

For example:

CM7 cores in CAT1C devices support Data Cache. Data Cache line is 32 bytes. User needs to make sure that the source and destination buffer pointers and the config structure pointers passed to the following functions points to 32 byte aligned data. Cy_DMAC_Channel_SetDescriptor, Cy_DMAC_Descriptor_SetNextDescriptor, Cy_DMAC_Descriptor_SetSrcAddress, Cy_DMAC_Descriptor_SetDstAddress. User can use CY_ALIGN(32) macro for 32 byte alignment. User needs to clean the following data elements from the cache and invalidate before accessing them. source and destination buffers and descriptor structure.

See the DMAC chapter of the device technical reference manual (TRM).

| Version | Changes | Reason for Change |

|---|---|---|

| 1.40 | Added new API Cy_DMAC_Channel_IsEnabled. | New devices support. |

| 1.30.1 | Minor Documentation update for cache usage on CM7. | Documentation enhancement. |

| 1.30 | Update to configure DMAC on core CM7. | Support for new product family. |

| 1.20 | Fixed MISRA 2012 violations. | MISRA 2012 compliance. |

| 1.10.1 | Minor documentation updates. | Documentation enhancement. |

| 1.10 | The Cy_DMAC_Channel_ClearInterrupt is changed. | Minor defect fixing. |

| 1.0 | The initial version. |

API Reference | |

| Macros | |

| Interrupt Masks | |

| Functions | |

| Data Structures | |

| Enumerated Types | |