Implementation specific interface for using the Clock driver.

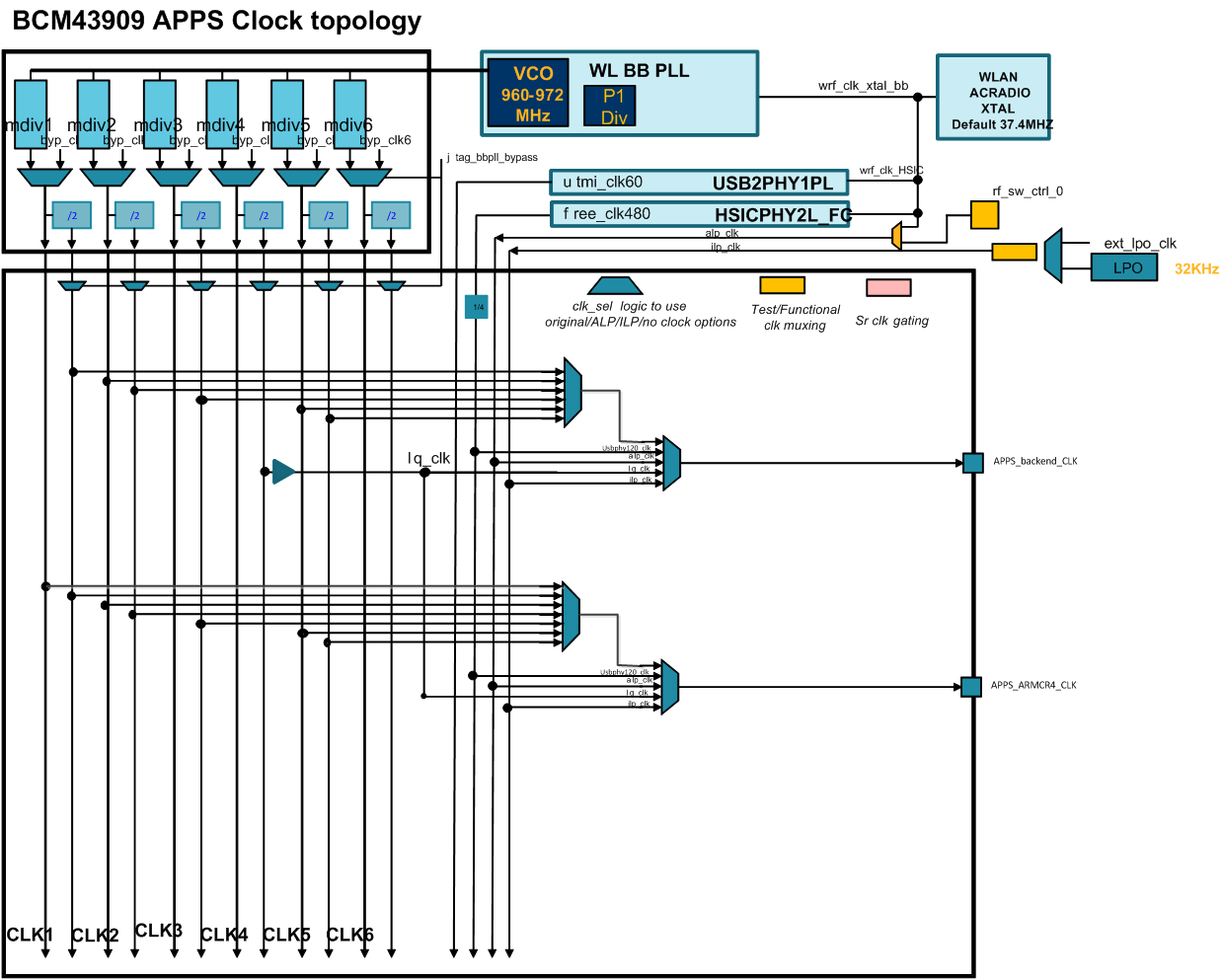

These items, while usable within the HAL, are not necessarily portable between devices. The diagram below shows how the clocks relate to each other. This is a superset of what is available. See the device specific Data Sheet for the exact set of clocks that are available on a specific device.

The system clocks are initialized in the cybsp_init() function.

Variables | |

| const cyhal_clock_t | CYHAL_CLOCK_ALP |

| Active Low Power (ALP): Supplied by an internal or external oscillator. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_ALP |

| Active Low Power (ALP): Supplied by an internal or external oscillator. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_HT |

| High Throughput (HT): Supplied by an on-chip PLL. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_HT |

| High Throughput (HT): Supplied by an on-chip PLL. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_ILP |

| Idle Low Power (ILP): Generated by either an internal or external low-power oscillator (LPO) or by dividing the ALP clock frequency by a programmable value. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_ILP |

| Idle Low Power (ILP): Generated by either an internal or external low-power oscillator (LPO) or by dividing the ALP clock frequency by a programmable value. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_LPO |

| Low Power Oscillator (LPO): Internal/external 32 kHz clock source for low-power mode. | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_LPO |

| Low Power Oscillator (LPO): Internal/external 32 kHz clock source for low-power mode. | |

| const cyhal_clock_t | CYHAL_CLOCK_XTAL |

| WLAN ACRADIO Crystal (XTAL): External 37.4 MHz clock source for active mode. | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_XTAL |

| WLAN ACRADIO Crystal (XTAL): External 37.4 MHz clock source for active mode. | |

| const cyhal_clock_t | CYHAL_CLOCK_BB_PLL |

| Baseband phase-Locked Loop (BB PLL): The baseband PLL provides digital clocks to the HT, Backplane and the digital cores (including WLAN domain). More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_BB_PLL |

| Baseband phase-Locked Loop (BB PLL): The baseband PLL provides digital clocks to the HT, Backplane and the digital cores (including WLAN domain). More... | |

| const cyhal_clock_t | CYHAL_CLOCK_AUDIO_PLL |

| Audio phase-Locked Loop (AUDIO PLL): The Audio PLL provides MCLK for I2S interfaces and audio timer clocks for ASCU. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_AUDIO_PLL |

| Audio phase-Locked Loop (AUDIO PLL): The Audio PLL provides MCLK for I2S interfaces and audio timer clocks for ASCU. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_USB_PLL |

| USB phase-Locked Loop (USB PLL): The USB PLL provides clocks for the USB. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_USB_PLL |

| USB phase-Locked Loop (USB PLL): The USB PLL provides clocks for the USB. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_HSIC_PLL |

| HSIC phase-Locked Loop (PLL): The HSIC PLL provides clocks for the HSIC. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_HSIC_PLL |

| HSIC phase-Locked Loop (PLL): The HSIC PLL provides clocks for the HSIC. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_WLAN_PLL |

| WLAN phase-Locked Loop (WLAN PLL): The WLAN radio PLL provides the RF LO, plus ADC and DAC clocks. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_WLAN_PLL |

| WLAN phase-Locked Loop (WLAN PLL): The WLAN radio PLL provides the RF LO, plus ADC and DAC clocks. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_CPU |

| CPU : Clock for the apps ARM CR4 core. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_CPU |

| CPU : Clock for the apps ARM CR4 core. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_BACKPLANE |

| Backplane : Provides the clock for peripherals and CPU. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_BACKPLANE |

| Backplane : Provides the clock for peripherals and CPU. More... | |

| const cyhal_clock_t | CYHAL_CLOCK_FAST_UART |

| Fast UART : Dedicated clock source for fast uart. More... | |

| const cyhal_resource_inst_t | CYHAL_CLOCK_RSC_FAST_UART |

| Fast UART : Dedicated clock source for fast uart. More... | |

|

extern |

Active Low Power (ALP): Supplied by an internal or external oscillator.

This clock is requested by cores when accessing backplane registers in other cores or when performing minor computations. When an external crystal is used to provide reference clock, ALP clock frequency is determined by the frequency of the external oscillator. A 37.4 MHz reference clock is recommended.

|

extern |

Active Low Power (ALP): Supplied by an internal or external oscillator.

This clock is requested by cores when accessing backplane registers in other cores or when performing minor computations. When an external crystal is used to provide reference clock, ALP clock frequency is determined by the frequency of the external oscillator. A 37.4 MHz reference clock is recommended.

|

extern |

High Throughput (HT): Supplied by an on-chip PLL.

This clock is requested by cores when they transfer blocks of data to or from memory, perform computation-intensive operations, or need to meet the requirements of external devices. Cores that cannot tolerate operations at less than the High Throughput (HT) clock frequency, such as the memory controller, may assert the HT clock request continuously.

|

extern |

High Throughput (HT): Supplied by an on-chip PLL.

This clock is requested by cores when they transfer blocks of data to or from memory, perform computation-intensive operations, or need to meet the requirements of external devices. Cores that cannot tolerate operations at less than the High Throughput (HT) clock frequency, such as the memory controller, may assert the HT clock request continuously.

|

extern |

Idle Low Power (ILP): Generated by either an internal or external low-power oscillator (LPO) or by dividing the ALP clock frequency by a programmable value.

Use of this clock maximizes power savings during idle states.

|

extern |

Idle Low Power (ILP): Generated by either an internal or external low-power oscillator (LPO) or by dividing the ALP clock frequency by a programmable value.

Use of this clock maximizes power savings during idle states.

|

extern |

Baseband phase-Locked Loop (BB PLL): The baseband PLL provides digital clocks to the HT, Backplane and the digital cores (including WLAN domain).

Nominal frequency is 960.1 MHz clock.

|

extern |

Baseband phase-Locked Loop (BB PLL): The baseband PLL provides digital clocks to the HT, Backplane and the digital cores (including WLAN domain).

Nominal frequency is 960.1 MHz clock.

|

extern |

Audio phase-Locked Loop (AUDIO PLL): The Audio PLL provides MCLK for I2S interfaces and audio timer clocks for ASCU.

Note that this clock is currently not supported.

|

extern |

Audio phase-Locked Loop (AUDIO PLL): The Audio PLL provides MCLK for I2S interfaces and audio timer clocks for ASCU.

Note that this clock is currently not supported.

|

extern |

USB phase-Locked Loop (USB PLL): The USB PLL provides clocks for the USB.

Note that this clock is currently not supported.

|

extern |

USB phase-Locked Loop (USB PLL): The USB PLL provides clocks for the USB.

Note that this clock is currently not supported.

|

extern |

HSIC phase-Locked Loop (PLL): The HSIC PLL provides clocks for the HSIC.

Note that this clock is currently not supported.

|

extern |

HSIC phase-Locked Loop (PLL): The HSIC PLL provides clocks for the HSIC.

Note that this clock is currently not supported.

|

extern |

WLAN phase-Locked Loop (WLAN PLL): The WLAN radio PLL provides the RF LO, plus ADC and DAC clocks.

Note that this clock is currently not supported.

|

extern |

WLAN phase-Locked Loop (WLAN PLL): The WLAN radio PLL provides the RF LO, plus ADC and DAC clocks.

Note that this clock is currently not supported.

|

extern |

CPU : Clock for the apps ARM CR4 core.

It can be sourced either by ARM(own path from HT) or Backplane clock. If using 320 MHz or 480 MHz, the clock source will be ARM (own path from HT). Otherwise the Backplane clock is used. Modifying the CPU frequency will also change the backplane frequency and hence it will also affect peripherals that run off of the backplane clock. The backplane clock frequency is the same as the CPU frequency. If running at 320 MHz or 480 MHz, the backplane frequency is 160 MHz.

|

extern |

CPU : Clock for the apps ARM CR4 core.

It can be sourced either by ARM(own path from HT) or Backplane clock. If using 320 MHz or 480 MHz, the clock source will be ARM (own path from HT). Otherwise the Backplane clock is used. Modifying the CPU frequency will also change the backplane frequency and hence it will also affect peripherals that run off of the backplane clock. The backplane clock frequency is the same as the CPU frequency. If running at 320 MHz or 480 MHz, the backplane frequency is 160 MHz.

|

extern |

Backplane : Provides the clock for peripherals and CPU.

It is sourced from HT. Active domain peripherals that do not have dedicated PLLs are either clocked directly from ALP or from the backplane. Thus it is a shared resource and care must be taken when changing this clock. Modifying the backplane frequency also affects the CPU. The backplane frequency is upper bound at 160 MHz

|

extern |

Backplane : Provides the clock for peripherals and CPU.

It is sourced from HT. Active domain peripherals that do not have dedicated PLLs are either clocked directly from ALP or from the backplane. Thus it is a shared resource and care must be taken when changing this clock. Modifying the backplane frequency also affects the CPU. The backplane frequency is upper bound at 160 MHz

|

extern |

Fast UART : Dedicated clock source for fast uart.

Derived from BB_PLL and fixed at 160 MHz.

|

extern |

Fast UART : Dedicated clock source for fast uart.

Derived from BB_PLL and fixed at 160 MHz.