The PRA driver is used to protect the system from invalid configurations that could potentially cause the system to be unstable or indirectly allow access to registers and memory that are protected. This is done using several methods:

Allow access to non-critical registers that are protected by a fixed PPU.

On PSoC 64 devices, secure firmware protects entire regions of registers with the fixed PPUs, however there are some registers within that regions that should not be protected but, are protected due to fixed PPU granularity.

The list of the registers that can be accessed by PRA driver directly is defined in the cy_pra.h file with the CY_PRA_INDX_ prefix.

Most PDL drivers are not affected or use the PRA driver. Only the following PDL drivers are affected by this driver:

The execution time of the functions that access the protected registers is increased on the PSoC 64 devices because the access is performed on Cortex-M0+ via the IPC command (both CPU cores run at 8 MHz):

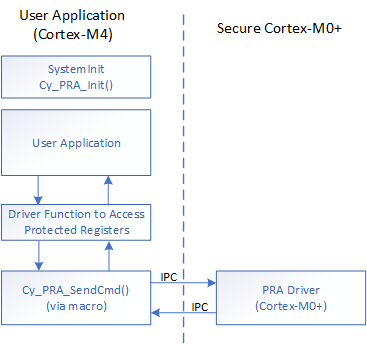

The PRA driver uses an IPC channel to transfer register data between the user application running on the Cortex-CM4 and the secure Cortex-CM0+ CPU. The secure processor performs the data validation and correct register write sequence to ensure proper stable operation of the system. Function status and requested data is also returned via the IPC channel.

The PDL driver that accesses protected registers, generates request to the PRA driver and it passes request over the IPC to secure Cortex-M0+, where request is validated and executed, and, then, reports result back to the driver on Cortex-M4 side.

For PSoC 64 device, device configuration (like system clock settings and power modes) is applied on the secure Cortex-M0+. The device configuration structure cy_stc_pra_system_config_t is initialized with Device Configurator and passed to the secure Cortex-M0+ for validation and register the update in the cybsp_init() function.

If PDL is used in Standalone mode without Board Support Package (BSP), do the following:

See the device technical reference manual (TRM) reference manual (TRM) for the list of the protected registers.

The LVD driver specific deviations:

| MISRA Rule | Rule Class (Required/Advisory) | Rule Description | Description of Deviation(s) |

|---|---|---|---|

| 13.7 | R | Boolean operations with invariant results are not permitted. | False positive. Cy_PRA_SendCmd() compiled for Cortex-M4 has a shared variable, which is modified by the Cortex-M0+ application, but the analysis tool is not aware of this fact. |

| 14.1 | R | No unreachable code. | False positive. Cy_PRA_SendCmd() compiled for Cortex-M4 has a shared variable, which is modified by the Cortex-M0+ application and used in a condition statement, but the analysis tool is not aware of this fact. |

| 14.7 | R | A function has a single exit point at the end of the function. | There are a few functions with multiple exit points implemented to simplify functions design. |

| 19.13 | A | Do not use the # and ## operators. | The ## preprocessor operator is used in macros to form the field mask. |

| 20.3 | R | Check the validity of values passed to library functions. | The additional check to eliminate the possibility of accessing the beyond array in Cy_PRA_ProcessCmd(). |

| Version | Changes | Reason for Change |

|---|---|---|

| 2.0 | Added PSoC 64 CYB06xx7 devices support. | New devices support. |

| Updated Cy_PRA_Init() to compare the major and minor version of the PRA driver on the Cortex-M0+ and Cortex-M4 sides and halt Cortex-M4 if the versions are different. | Ensure that the same PRA driver version is used on the Cortex-M0+ and Cortex-M4 sides. | |

| Fixed the location of the cy_stc_pra_system_config_t description in the documentation. | Documentation update. | |

| Corrected the reference to the SysTick (ARM System Timer) function with the limitation description - Cy_SysTick_SetClockSource(). | Documentation update. | |

| The state of the following clocks changes only when the requested state differs from the actual state in the hardware: HF1-HF5, TIMER, PUMP, BLE_ECO, ILO, PILO, and WCO. | Improved the Cy_PRA_SystemConfig() function execution time. | |

| Renamed altHfFreq to altHFclkFreq in cy_stc_pra_system_config_t. | Eliminated the naming conflict with the SysClk driver. | |

| 1.0 | Initial version |

API Reference | |

| Macros | |

| Functions | |

| Enumerated Types | |

| Data Structures | |